# Deductive Verification of Real-World C++ Weak-Memory Programs

Pascal Wiesmann Supervised by Dr. Alexander J. Summers

June 2, 2019

#### Abstract

In this work we provide a high-level and intuitive logic for the verification of weak memory C++ programs. The logic is based on FSL++[4] and improves it in two crucial aspects. First, it significantly simplifies the task of writing the specification. Second, it is more suitable for automating verification. We also provide a tool that verifies weak-memory C++ programs using our new logic. The program and the specifications are encoded into Viper in such a way that they can then be automatically verified.

# Contents

| 1 | Intr                                                        | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                 |

|---|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 2 | <b>Bac</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | kgroundWeak MemoryData racesAtomics and SynchronizationRelaxed Separation LogicFenced Separation Logic (FSL)FSL++Entity Fractional Counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6<br>7<br>7<br>8<br>9<br>10<br>10 |

| 3 | Tok                                                         | en-based Reasoning for Weak Memory Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11                                |

| 0 | 3.1                                                         | Tokens         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <th>12</th> | 12                                |

|   | 3.2                                                         | Splitting and Merging Tokens                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                |

|   | 3.3                                                         | The source of the tokens                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                |

|   | 3.4                                                         | Generating tokens from the source and merging tokens back in .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13                                |

|   | 3.5                                                         | Rules to get the write permission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14                                |

|   | 3.6                                                         | The relation of tokens and the EFC monoid $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14                                |

|   | 3.7                                                         | Modalities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                |

|   | 3.8                                                         | The $up$ -modality $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                |

|   | 3.9                                                         | Rules for Acquire Fences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                |

|   | 3.10                                                        | Rules for Release Fences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                |

|   | 3.11                                                        | The life of a non-atomic variable and its tokens                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                |

|   | 3.12                                                        | Specification Syntax for Token-based Proofs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                                |

|   |                                                             | 3.12.1 Source code annotations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                                |

|   |                                                             | 3.12.2 Using Proof Rules from the RSL logics on IDF-Style As-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                |

|   |                                                             | sertions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19                                |

| 4 | Aut                                                         | omation of Token-based Proofs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                |

|   | 4.1                                                         | Merging and splitting resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22                                |

|   | 4.2                                                         | Method calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                |

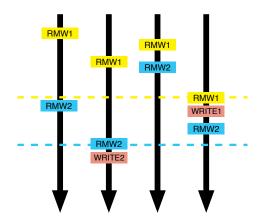

|   | 4.3                                                         | Release-acquire RMW operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22                                |

|   | 4.4                                                         | Generalized RMW operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23                                |

| <b>5</b> | $\mathbf{Pro}$                                                                              | ofs for example programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>25</b>                                                                                                                                                 |

|----------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 5.1                                                                                         | Spinlock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26                                                                                                                                                        |

|          |                                                                                             | 5.1.1 try_lock_shared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                                                                                                                        |

|          |                                                                                             | 5.1.2 unlock_shared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28                                                                                                                                                        |

|          |                                                                                             | 5.1.3 try_lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29                                                                                                                                                        |

|          |                                                                                             | 5.1.4 unlock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29                                                                                                                                                        |

|          |                                                                                             | 5.1.5 unlock_and_lock_shared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30                                                                                                                                                        |

|          | 5.2                                                                                         | Barrier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30                                                                                                                                                        |

|          |                                                                                             | 5.2.1 Proof $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                                                                                                                                        |

|          | 5.3                                                                                         | ARC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33                                                                                                                                                        |

|          |                                                                                             | 5.3.1 Constructor $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34                                                                                                                                                        |

|          |                                                                                             | 5.3.2 read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34                                                                                                                                                        |

|          |                                                                                             | 5.3.3 clone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35                                                                                                                                                        |

|          |                                                                                             | 5.3.4 drop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                                                                                                                        |

|          | 5.4                                                                                         | ARC version 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                                                                        |

|          |                                                                                             | 5.4.1 Constructor $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36                                                                                                                                                        |

|          |                                                                                             | 5.4.2 read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                                                                                                                        |

|          |                                                                                             | 5.4.3 clone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                                                                                                        |

|          |                                                                                             | 5.4.4 drop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38                                                                                                                                                        |

|          | 5.5                                                                                         | ARC comparison to FSL++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                                                                                                        |

|          |                                                                                             | 5.5.1 FSL++ proof of drop function $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                                                                                                        |

| ~        | G                                                                                           | tax for C++ input programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                                                                                                                                                        |

| 6        | Syn                                                                                         | tax for $O_{++}$ input programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                                                                                                                                                        |

|          | -                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                                                                                                                                                        |

| 6<br>7   | C+-                                                                                         | + to Viper encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42                                                                                                                                                        |

|          | C+-<br>7.1                                                                                  | + to Viper encoding<br>Ghost locations and modalities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>42</b><br>42                                                                                                                                           |

|          | C+-                                                                                         | + to Viper encoding<br>Ghost locations and modalities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>42</b><br>42<br>43                                                                                                                                     |

|          | C+-<br>7.1                                                                                  | + to Viper encoding<br>Ghost locations and modalities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>42</b><br>42<br>43<br>43                                                                                                                               |

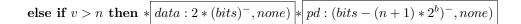

|          | C+-<br>7.1                                                                                  | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                      | <b>42</b><br>42<br>43                                                                                                                                     |

|          | C+-<br>7.1                                                                                  | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the</li> </ul>                                                                                                                                                                                                                                                                                                                                 | <b>42</b><br>42<br>43<br>43<br>43                                                                                                                         |

|          | C+-<br>7.1                                                                                  | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>42</b><br>42<br>43<br>43<br>43<br>43                                                                                                                   |

|          | C+-<br>7.1                                                                                  | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> </ul>                                                                                                                                                                                                                                                                                       | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>43                                                                                                       |

|          | C+-<br>7.1<br>7.2                                                                           | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> </ul>                                                                                                                                                                                                                                                        | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>45<br>45                                                                                                 |

|          | C+-<br>7.1<br>7.2<br>7.3                                                                    | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> </ul>                                                                                                                                                                                                                        | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>45<br>46                                                                                     |

|          | C+-<br>7.1<br>7.2<br>7.3<br>7.4                                                             | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> </ul>                                                                                                                                                                                            | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>45<br>46<br>48                                                                               |

|          | C+-<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5                                                      | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> </ul>                                                                                                                                                                       | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>45<br>46<br>48<br>48                                                                         |

|          | C+<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6                                                | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> </ul>                                                                                                                                                      | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>45<br>46<br>48<br>48<br>49                                                                   |

|          | C+<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7                                         | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> <li>Local variables</li> </ul>                                                                                                                             | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>45<br>46<br>48<br>48<br>49<br>49                                                             |

|          | C+-<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8                                 | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> <li>Methods</li> </ul>                                                                                                                                     | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>46<br>48<br>48<br>49<br>49<br>49                                                 |

|          | C+<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9                           | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> <li>Local variables</li> <li>Methods</li> <li>Assertions</li> </ul>                                                                                        | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>46<br>48<br>48<br>49<br>49<br>49<br>52                                                 |

|          | C+<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>7.10                   | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> <li>Methods</li> <li>Assertions</li> <li>Inhales and Exhales</li> </ul>                                                                                    | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>45<br>46<br>48<br>48<br>49<br>49<br>49<br>52<br>52                                           |

|          | C+-<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9<br>7.10<br>7.11          | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> <li>Methods</li> <li>Assertions</li> <li>Inhales and Exhales</li> <li>Fences</li> </ul>                                                                    | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>46<br>48<br>48<br>49<br>49<br>52<br>52<br>52<br>52                                           |

|          | $C+-7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7 \\ 7.8 \\ 7.9 \\ 7.10 \\ 7.11 \\ 7.12 \\$ | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> <li>Local variables</li> <li>Methods</li> <li>Assertions</li> <li>Inhales and Exhales</li> <li>Read-Modify-Write Operations</li> </ul>                     | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>46<br>48<br>48<br>49<br>49<br>49<br>52<br>52<br>52<br>52<br>53 |

|          | $C+-7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7 \\ 7.8 \\ 7.9 \\ 7.10 \\ 7.11 \\ 7.12 \\$ | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> <li>Atomics</li> <li>Assertions</li> <li>Inhales and Exhales</li> <li>Fences</li> <li>Read-Modify-Write Operations</li> <li>Location Invariants</li> </ul> | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>45<br>46<br>48<br>49<br>49<br>49<br>52<br>52<br>52<br>53<br>53 |

|          | $C+-7.1 \\ 7.2 \\ 7.3 \\ 7.4 \\ 7.5 \\ 7.6 \\ 7.7 \\ 7.8 \\ 7.9 \\ 7.10 \\ 7.11 \\ 7.12 \\$ | <ul> <li>+ to Viper encoding</li> <li>Ghost locations and modalities</li> <li>Encoding Tokens</li> <li>7.2.1 Encoding the Token Counting</li> <li>7.2.2 Encoding the Permission Sum Associated with the Tokens</li> <li>7.2.3 Encoding the Relation between the Token Count and the Permission</li> <li>7.2.4 Inhaling Tokens</li> <li>7.2.5 Exhaling Tokens</li> <li>Encoding a C++ program</li> <li>Field declarations</li> <li>Non-Atomics</li> <li>Atomics</li> <li>Local variables</li> <li>Methods</li> <li>Assertions</li> <li>Inhales and Exhales</li> <li>Read-Modify-Write Operations</li> </ul>                     | <b>42</b><br>42<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>43<br>45<br>45<br>46<br>48<br>48<br>49<br>49<br>49<br>52<br>52<br>52<br>52<br>53 |

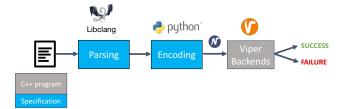

| 8 | Veri  | fication Tool for Weak Memory Programs    | <b>58</b> |

|---|-------|-------------------------------------------|-----------|

|   | 8.1   | Parser                                    | 58        |

|   | 8.2   | Encoder                                   | 58        |

|   | 8.3   | Benchmarks                                | 59        |

| 9 | Con   | clusion and Future Work                   | 60        |

|   | 9.1   | Conclusion                                | 60        |

|   | 9.2   | Future Work                               | 60        |

| A | cknow | vledgments                                | 62        |

| A | Mor   | e details on Viper encoding               | 65        |

|   | A.1   | Fences                                    | 65        |

|   | A.2   | exhaleSource definition                   | 66        |

|   | A.3   | Basic Viper definitions                   | 68        |

|   | A.4   | Parallel Heaps                            | 69        |

|   |       | Barrier without precondition              | 70        |

|   |       | A.5.1 Specification                       | 70        |

|   |       | A.5.2 Proof outline                       | 71        |

|   |       | A.5.3 Explanations                        | 71        |

|   | A.6   | Full details for Atomic Reference Counter | 73        |

|   | -     | A.6.1 $C$ ++ Code                         | 73        |

|   |       | A.6.2 Generated Viper Code                | 74        |

# Chapter 1

# Introduction

The performance that can be achieved by using low-level concurrent C++ is often desired in library-programs. For the sake of performance, the memory model that was introduced in C++11 provides very weak guarantees regarding concurrency: this is the reason why it is called *weak memory*. Weak memory programs are very hard to write, as well as to test, for at least two reasons. First, the weak memory semantics allow even more executions of a program than all the possible sequential interleavings of the threads (which might already be many). Second, some of these executions might be extremely rare and it would be very unlikely to observe them using random test-cases. However, such low-level libraries are not only hard to write and to test, it is also absolutely crucial that they are reliable, because they are used in many complex software projects. Therefore, not even extremely rare failures are acceptable. Subtle bugs in the libraries may affect all of these projects in ways which are hard and frustrating to debug. In practice, these libraries are tested extensively, which is very time-consuming and still, one cannot be 100% sure that the program always is correct. Formal proofs, on the other hand, are also expensive, but they provide something very desirable which is usually impossible to achieve with testing: a guarantee that the program is correct in *all* scenarios.

Several logics for reasoning about weak memory programs have been proposed. To our knowledge, the main ones are RSL [12], FSL [3] and FSL++ [4] (both extensions of RSL) and GPS [11]. In this thesis, we focus on RSL and its extensions (collectively referred to as *RSL logics*). RSL and FSL are easier to automate than FSL++, but they are also much less expressive. In order to encode real world programs, a logic with an expressiveness similar to that of FSL++ is required. The problem with FSL++ is that the high flexibility of the encoding makes it hard to automate proofs. Attempts to define a logic that is possibly slightly less flexible than FSL++, but makes automation easier, have been made [7] but not yet compiled to a finished proposal.

A prototype tool for the automated verification of weak memory programs has been published [10]. It encodes large fractions of RSL and FSL into Viper [6], a language for which reliable and established verifiers exist. However, RSL and FSL only allow reasoning about individual atomic accesses in isolation. This is often not sufficient for the verification of real-world programs [4]. The reason is that in a particular library implementation, identical operations can have different meanings for verification, depending on what happened earlier in the program. In FSL++, ghost state makes it possible to artificially remember what happened earlier in the program, even when this is not possible to determine by looking at the program state.

This thesis addresses many of the shortcomings of existing logics and tools. Our main contributions are: (1) a high-level specification language for weak memory C++, (2) corresponding proof rules, (3) proofs for example programs that show the effectiveness of our system, (4) a tool that encodes our specification language and a subset of C++ into Viper, a framework for deductive verification.

# Chapter 2

# Background

# 2.1 Weak Memory

In his book The C++ programming language, Bjarne Stroustrup, the creator of C++, writes "Most programmers do not need to understand a memory model at all and can think of reorderings as amusing curiosities" and goes on to say "as sensible and productive programmers, we stay away from the lowest levels of software whenever we can. Leave those for the experts and enjoy the higher levels that those experts provide for you." [9]

If the typical professional software engineer should not have to worry about memory models, the code which experts provide for managing these models has to be absolutely bug-free. This does not mean that programmers do not have to think about parallel programming in general. It just means that most programmers should use library implementations of locks and other synchronization mechanisms (written by experts), which already take care of the relevant weak memory issues.

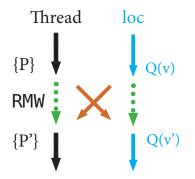

Weak memory models allow executions of multi-threaded programs that are not sequentially consistent. This means that the execution cannot be explained by a sequential interleaving of all operations. Consider the example in Figure 2.1. We assume the variables are all initialized before the functions are executed and ignore potential data races. Assuming sequential consistency, the resulting values (x, y) can be (0, 1), (0, 1) or (1, 1). An execution resulting in (0, 0) is not possible with a sequentially consistent memory model, but weaker memory models might allow it.

Achieving sequential consistency would lead to a considerable overhead in modern hardware. One reason is the hierarchical architecture of the caches that are used to speed up memory accesses. An operation takes effect on the local cache of a core long before it is visible for other cores. Sequentially consistent memory models require to synchronize the caches with the main memory more often than weaker memory models, which is expensive in terms of performance.

```

// thread 2:

int c = 0;

extern int b;

int f1()

{

c = 1; // A

int x = b; // B

return x;

}

// thread 2:

int b = 0;

extern int c;

int f2()

{

b = 1; // C

int y = c; // D

return y;

}

```

Figure 2.1: Example adapted from [9]

# 2.2 Data races

In C++, memory accesses can be atomic or non-atomic. Non-atomic accesses lead to undefined behavior in the semantics of C++ if two accesses are executed at the same time and at least one of them is a write. This is called a data race. One way to prevent undefined behavior while using non-atomic accesses is to protect them using synchronization libraries. These libraries are implemented using atomic operations.

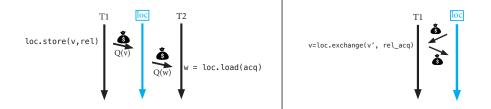

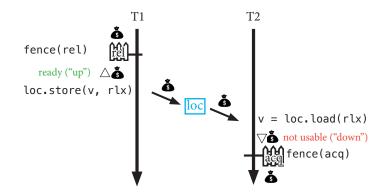

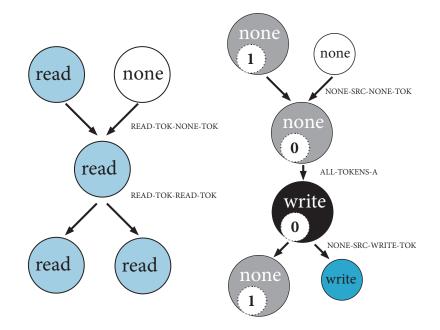

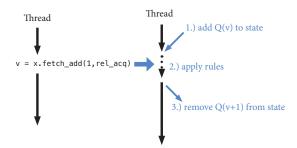

# 2.3 Atomics and Synchronization

The C++ semantics guarantee that atomic operations by multiple threads are always ordered, even if multiple threads try to execute atomic operations simultaneously. In other words, atomic accesses are allowed to race. Atomic accesses are much slower than non-atomic accesses, therefore using atomic operations on large shared data would be inefficient. Atomic operations are not only safe themselves, they can also be used to synchronize other memory accesses. Efficient library implementations often protect large amounts of shared data using atomic operation on a few small, dedicated memory locations (e.g. simple boolean flags or integer counters). Atomic operations have a synchronization parameter that can be set to e.g. memory order release (release), memory order acquire (acquire) or memory order relaxed. This parameter is also referred to as the *memory order* of an atomic operation. If all threads perceive a certain release operation on a memory location before an *acquire* operation on the same location, we get certain guarantees with respect to the order in which memory operations are perceived: All threads will perceive the effects of operations preceding the release operation before the effects of subsequent operations of the acquire operation. This means that non-atomic operations before (and in the same thread as) the release operation will not race with non-atomic operations after (and in the same thread as) the acquire operation. The same kind of synchronization cannot be achieved using relaxed operations.

# 2.4 Relaxed Separation Logic