# Network and Memory Abstractions on FPGAs for Distributed Applications.

Dario Korolija, Zhenhao He, Gustavo Alonso Systems Group Department of Computer Science ETH Zurich, Switzerland

#### The tutorial

• Slides available at:

https://systems.ethz.ch/research/data-processing-on-modernhardware/hacc.html

- More tutorials available covering diverse use cases and technologies around FPGAs

- FPGA'23 tutorial on networking on FPGAs

- SIGMOD'23 tutorial on data processing on FPGAs

- Also information on the use of the HACC cluster, research papers, etc.

#### Schedule

- Introduction and Motivation

- Coyote: an open shell for FPGAs

- EasyNet: an open, 100 Gbs TCP/IP network stack

- ACCL: collective network communication for FPGA clusters

- Farview: Smart Disaggregated Memory

- Distributed inference: on recommendation systems

## The Hardware Era

#### Not a new concept ...

- 2011 Report

- Exponential growth for several decades

- Exponential growth no longer possible

- Switch to multicore and parallelism

- Energy consumption becomes an issue

- Multicore introduces parallelism that we do not know how to exploit well

- Situation will not change in near future

- Alternative is specialization

- Either somebody comes up with a new great invention or there is a problem

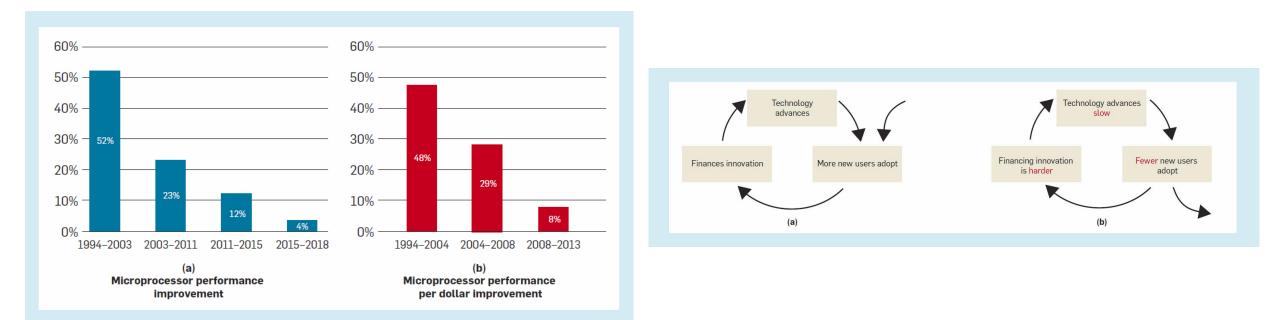

#### General purpose computing

Slow improvements lead to specialization

COMMUNICATIONS PF THE ACM HOME CURRENT ISSUE NEWS BLOGS OPINION RESEARCH PRACTICE CAREERS ARCHIVE VIDEOS Home / Magazine Archive / March 2021 (Vol. 64, No. 3) / The Decline of Computers as a General Purpose Technology / Full Text

The Decline of Computers as a General Purpose Technology

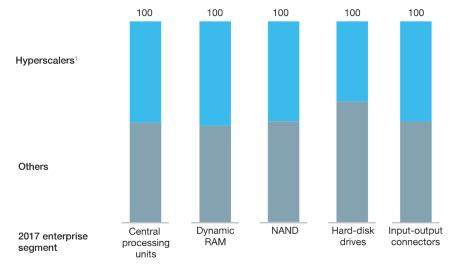

Hyperscalers, commanding a growing share of the market, are emerging as significant customers for many components.

#### Driving specialization

- The cloud is the big game changer:

- New business model

- Economies of scale

- Very large workloads

- Every hyper scaler is its own "Killer App"

- The scale makes many things feasible

- The gains have a very large multiplier

https://www.mckinsey.com/industries/technology-media-and-telecommunications/our-insights/how-high-tech-suppliers-are-responding-to-the-hyperscaler-opportunity

<sup>1</sup>Includes Alibaba, Alphabet, Amazon, Baidu, Facebook, Microsoft, and Tencent.

## Large deployment of FPGAs in the cloud – examples

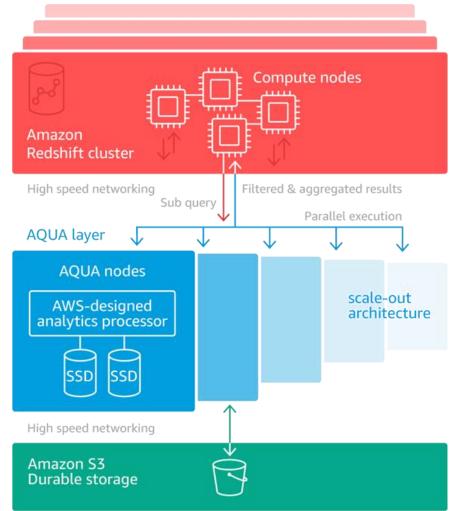

- FPGAs as smart accelerator for disaggregated resources

- Amazon AQUA

- https://aws.amazon.com/blogs/aws/new-aqua-advanced-query-accelerator-for-amazonredshift/

- Analytic engine with FPGAs

- Pushing computation closer to data

- Reduce CPU compute requirement

- Reduce network traffic

#### Data Compression (Microsoft Zipline/Corsica)

#### Corsica: A project zipline ASIC

Compression without compromise:

- High compression ratio

- Low latency

- Inline encryption, authentication

- High total throughput

| D                                 | isk write latency with Co                 |                                         |                   |

|-----------------------------------|-------------------------------------------|-----------------------------------------|-------------------|

| System and<br>network<br>overhead | Corsica does<br>the work                  | SSD<br>read/write                       | I Microson        |

|                                   | Corsica is 15-25 time:                    | aster than the CPU                      |                   |

| System and<br>network<br>overhead | CPU does the w<br>Compression   Encryptic | rk<br>  Authentication   Data integrity | SSD<br>read/write |

|                                   |                                           | Disk write latency today                |                   |

https://azure.microsoft.com/en-us/blog/improved-cloud-service-performance-through-asic-acceleration/

#### Emerging themes

- Reduced CPU utilization

- Accelerate common operations

- Accelerate the infrastructure supporting the system

- Processing data on the fly

- Near data processing (memory, storage, ...)

- On demand servers and functionality

### HACC cluster at ETH Zurich

Gustavo Alonso. Systems Group. D-INFK. ETH Zurich

#### Infrastructure – HACC cluster

- The Heterogeneous Accelerated Compute Clusters (HACC) program is a unique initiative to support novel research in adaptive compute acceleration for data center settings and high-performance computing (HPC).

- ETH Zurich HACC https://systems.ethz.ch/research/dataprocessing-on-modern-hardware/hacc.html

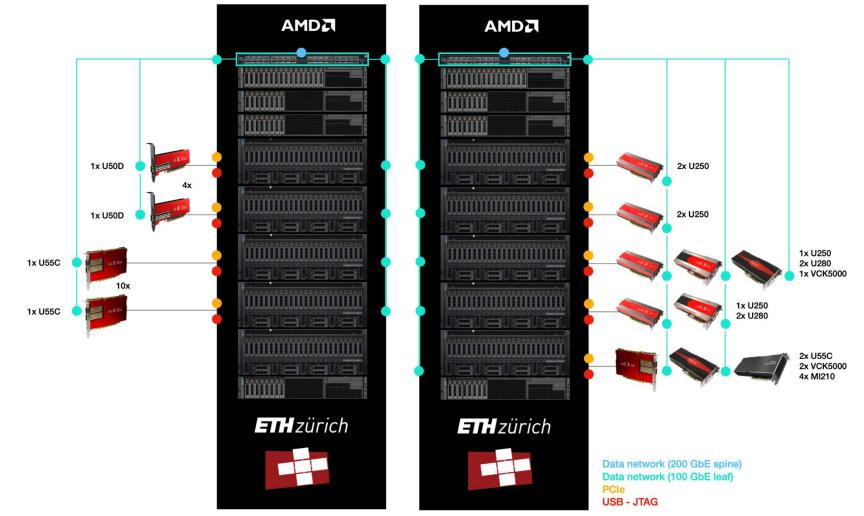

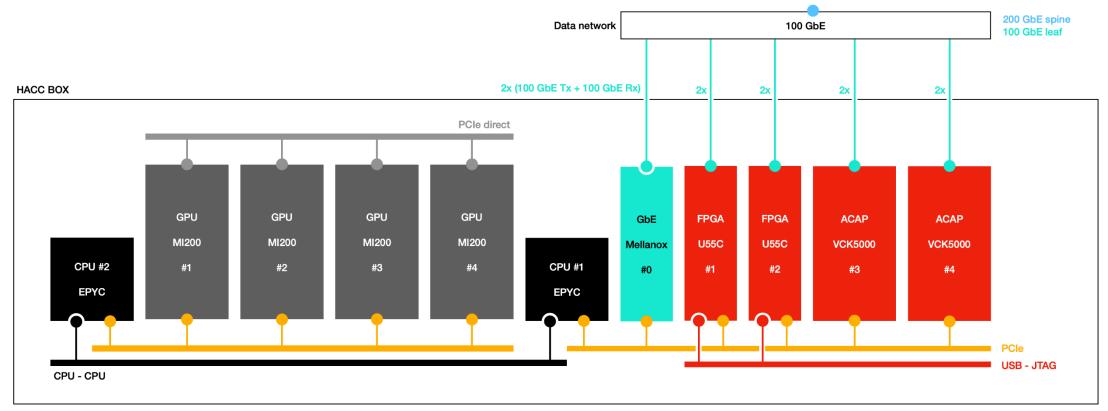

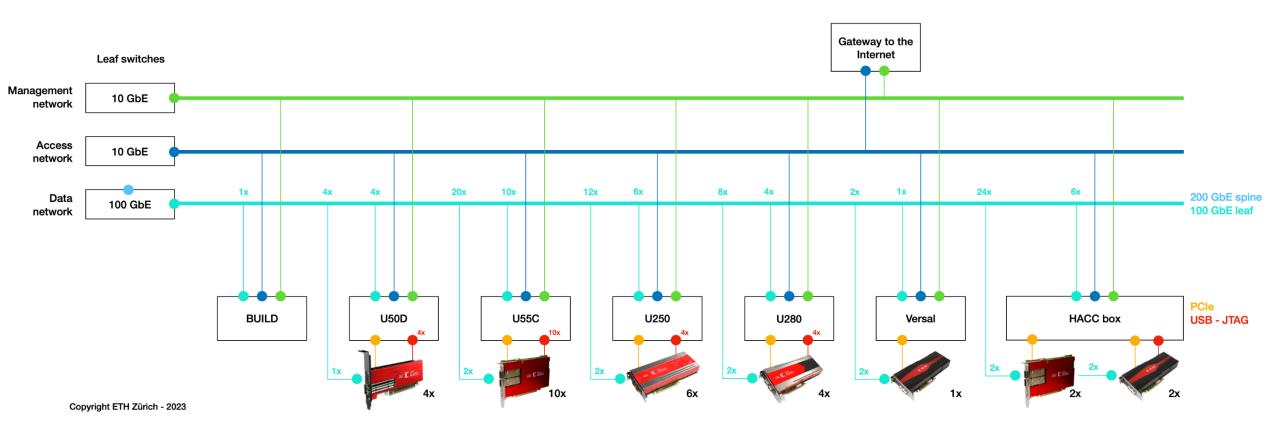

#### HACC Cluster

- Target: Facilitate practitioners and researchers exploring distributed applications on FPGA clusters

- FPGA clusters (HACC and Enzian)

- Data center standard infrastructure

- Frameworks and abstractions (Vitis and Coyote)

- Shell support and abstractions for in-network processing, disaggregated computation, distributed applications ...

- Systems and applications built on top

#### Introduction to HACC cluster

Copyright ETH Zürich - 2023

#### Overview (HACC heterogeneous boxes)

Copyright ETH Zürich - 2023

#### Overview

#### Booking system

- Reserving a specific VM/device for a specific period

- Maximum 5 hours per reservation

- During a reservation, only the selected user can connect to the VM/device

- User can choose different workflows when login

- Vitis workflow

- Coyote workflow

| AMDZ<br>XLLNX<br>Heterogeneous Accelerated Compute Clusters<br>University Research Partners<br>THIZURICH I ILLINOIS                              |             |    |    |     |    |    |    |    |             |          |    |                  |    |    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----|----|-----|----|----|----|----|-------------|----------|----|------------------|----|----|--|

| New Booking<br>all times are CET (Zurich, Switzerland)<br>Maximum booking time is 5 hours<br>Time range *<br>2023-02-06 13:29 - 2023-02-06 14:29 |             |    |    |     |    |    |    |    |             |          |    |                  |    |    |  |

|                                                                                                                                                  |             |    |    | Use | rs |    |    |    |             |          |    |                  |    |    |  |

|                                                                                                                                                  | Feb 2023    |    |    |     |    |    |    |    |             | Mar 2023 |    |                  |    |    |  |

|                                                                                                                                                  | Su          | Мо | Tu | We  | Th | Fr | Sa | Su | Mo          | ти       | We | Th               | Fr | Sa |  |

|                                                                                                                                                  |             |    |    |     |    |    |    | 26 | 27          | 28       |    |                  |    | 4  |  |

|                                                                                                                                                  |             | 6  |    | 8   | 9  | 10 |    |    | 6           |          | 8  | 9                | 10 |    |  |

|                                                                                                                                                  | 12          | 13 | 14 | 15  | 16 |    | 18 | 12 | 13          | 14       | 15 | <mark>1</mark> 6 |    | 18 |  |

|                                                                                                                                                  | 19          | 20 | 21 | 22  | 23 | 24 | 25 | 19 | 20          | 21       | 22 | 23               | 24 | 25 |  |

|                                                                                                                                                  | 26          | 27 | 28 |     |    |    | 4  | 26 | 27          | 28       | 29 | 30               | 31 |    |  |

|                                                                                                                                                  |             | 6  |    | 8   | 9  | 10 |    |    |             | 4        |    | 6                |    | 8  |  |

|                                                                                                                                                  | 13 🗸 : 29 🗸 |    |    |     |    |    |    |    | 14 💙 : 29 🎔 |          |    |                  |    |    |  |

#### User access

#### • Access requires registration

- ETH users contact Gustavo Alonso

- All others through AMD Xilinx (HACC program)

- Users get guest account at ETH (renewable)

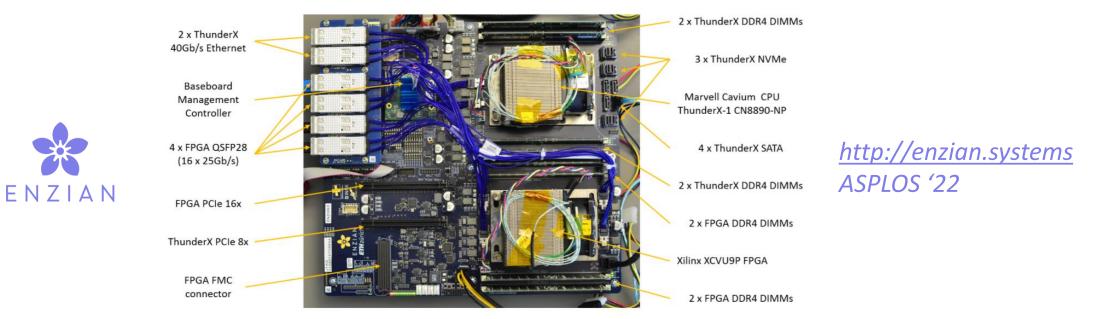

#### Enzian

- Research computer developed within the Systems Group at ETH

- Designed for computer systems software research, deliberately over-engineered

- Big server-class CPU closely coupled to a large FPGA, with ample main memory and network bandwidth on both sides

- Cache-coherent asymmetric NUMA system

## **Opportunities for FPGAs**

#### The future of accelerators

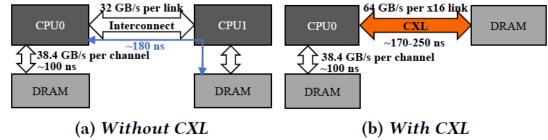

#### **TPP: Transparent Page Placement for CXL-Enabled Tiered Memory**

Hasan Al Maruf\*, Hao Wang<sup>†</sup>, Abhishek Dhanotia<sup>†</sup>, Johannes Weiner<sup>†</sup>, Niket Agarwal<sup>†</sup>, Pallab Bhattacharya<sup>†</sup>, Chris Petersen<sup>†</sup>, Mosharaf Chowdhury<sup>\*</sup>, Shobhit Kanaujia<sup>†</sup>, Prakash Chauhan<sup>†</sup>

University of Michigan\* Meta Inc.<sup>†</sup>

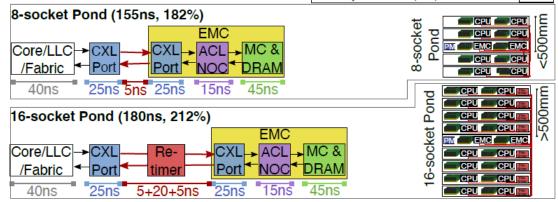

#### **Pond: CXL-Based Memory Pooling Systems for Cloud Platforms**

Huaicheng Li<sup>†</sup>, Daniel S. Berger<sup>\*‡</sup>, Stanko Novakovic<sup>\*</sup>, Lisa Hsu<sup>\*</sup>, Dan Ernst<sup>\*</sup>, Pantea Zardoshti\*, Monish Shah\*, Samir Rajadnya\*, Scott Lee\*, Ishwar Agarwal\*, Mark D. Hill<sup>\*°</sup>, Marcus Fontoura<sup>\*</sup>, Ricardo Bianchini<sup>\*</sup>

<sup>†</sup>Virginia Tech and CMU <sup>\*</sup>Microsoft Azure <sup>‡</sup>University of Washington <sup>°</sup>University of Wisconsin-Madison

METHORY CONTROLLER LINCTING & DTICIN

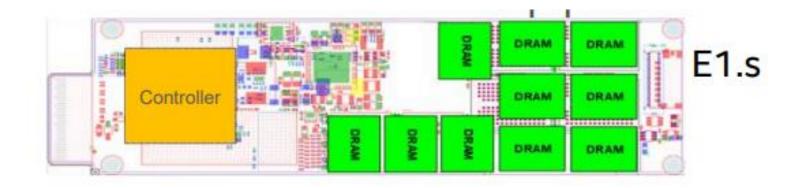

#### Disaggregated memory

- CXL memory will not be just memory

- It will be a module with a controller/processor that runs the protocol and manages the memory

- The controller is a great point to add near-data processing capabilities

## The tutorial in context

#### FPGAs in context

- We do not sell or market FPGAs

- FPGAs are the only way to explore:

- New architectural designs (even to the CPU design level, e.g., RISC-V)

- New computer architectures (near-memory processing, smart storage, smart NICs, accelerators, etc.)

- Processing of data streams at line rate

- Are FPGAs difficult?

- No, this is systems level programming, no less involved than writing your own database engine, operating system, etc.

- Yes, the tools are not what we are used to in the software world (by a long margin)

#### Goals

- Showcase open source tools available for researchers

- Facilitate research in data center applications and distributed computing

- Overall: encourage the community to explore this opportunity of achieving higher efficiency in data centers in a context where the new hardware is going to be available, even if for other reasons.