# Merging insights from artificial and biological neural networks

A competitive advantage for neuromorphic edge intelligence?

Charlotte Frenkel (<u>c.frenkel@tudelft.nl</u>)

Assistant Professor Dept. of Microelectronics, Delft University of Technology

> ETH Zurich March 20<sup>th</sup>, 2024

#### Outline

#### ① From neuroscience to AI and back again...

...which perspective? ...which starting point?

2 Why should we bother with neuroscience?

#### 3 How can we morph these questions into interesting engineering solutions?

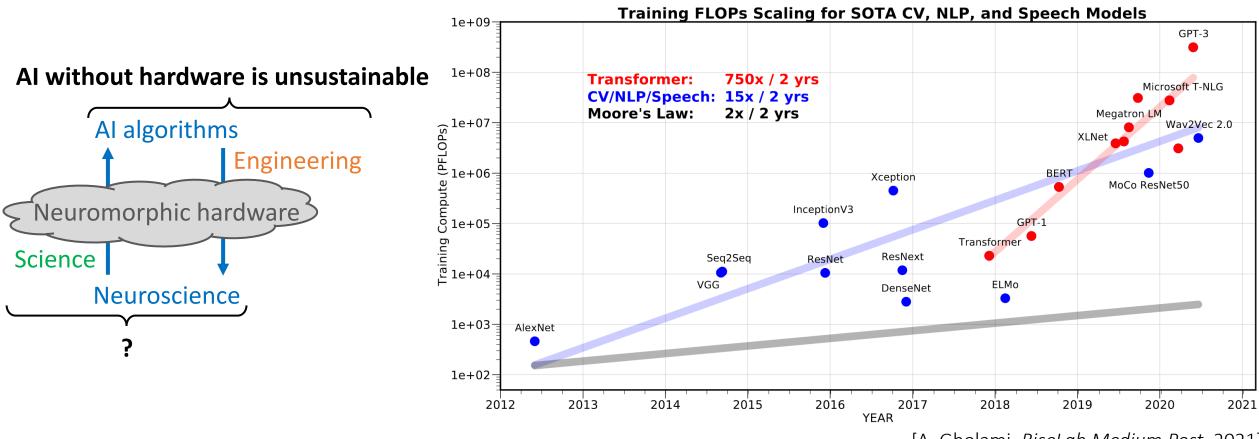

#### From neuroscience to AI and back again

Which starting point? Which perspective?

<sup>[</sup>A. Gholami, RiseLab Medium Post, 2021]

#### Outline

...which perspective?

...which starting point?

#### 2 Why should we bother with neuroscience?

#### 3 How can we morph these questions into interesting engineering solutions?

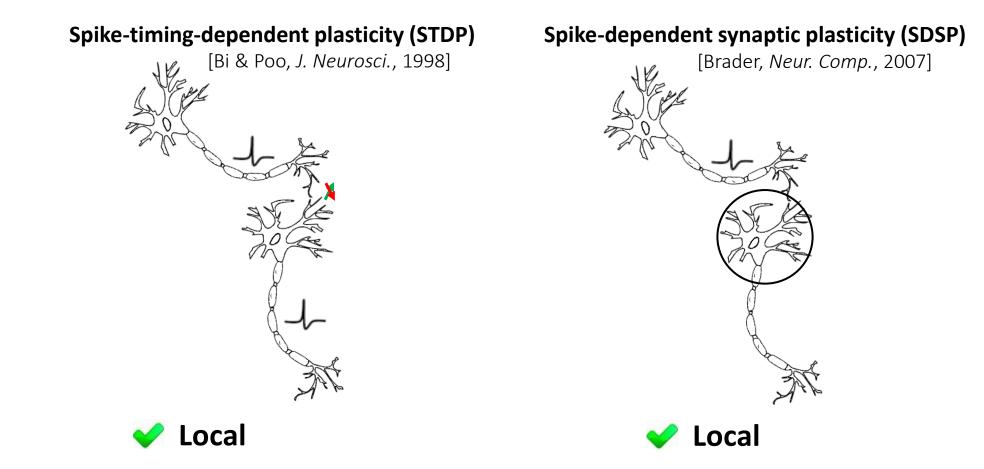

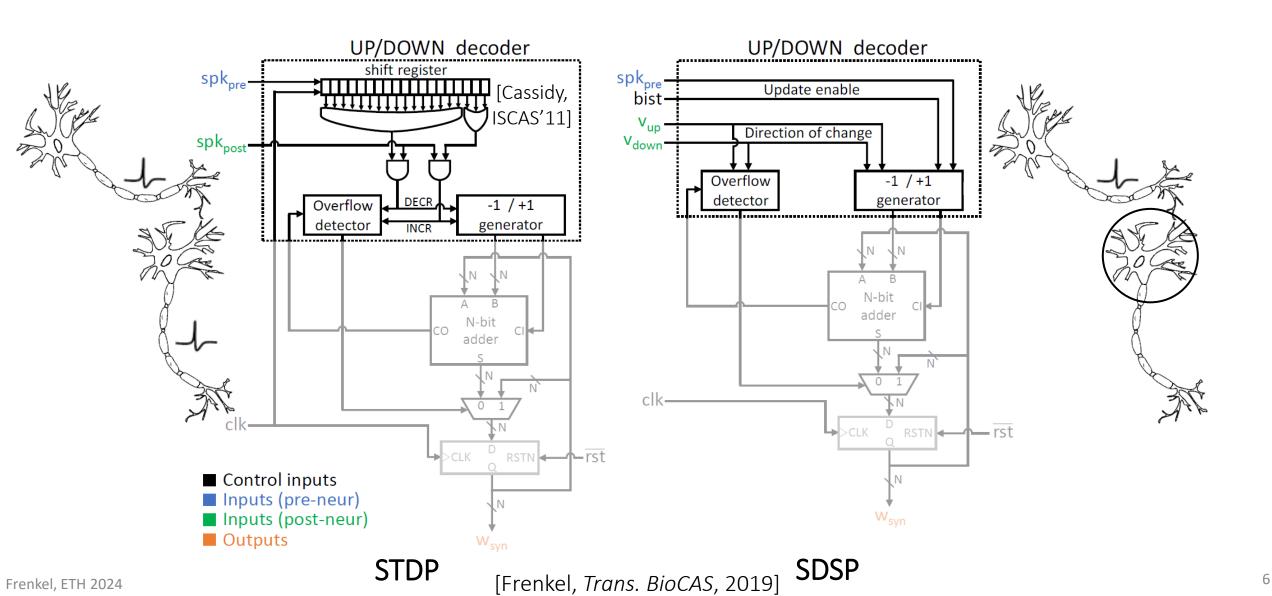

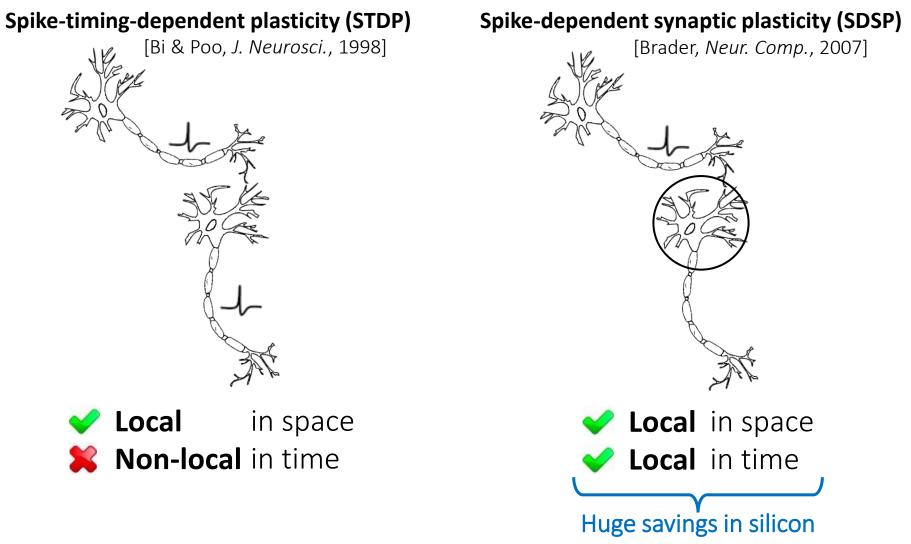

## Synaptic plasticity rules – Neuroscience as the starting point

Al algorithms

Frenkel, ETH 2024

## Synaptic plasticity rules – Neuroscience as the starting point

AI algorithms

Neuroscience

Digital synapse implementation

#### Synaptic plasticity rules – Neuroscience as the starting point The key perspective of data locality

[Clopath and Gerstner, Front. Syn. Neuro., 2010]

[Frenkel, TBioCAS, 2019]

AI algorithms

# Synaptic plasticity rules – Neuroscience as the starting point

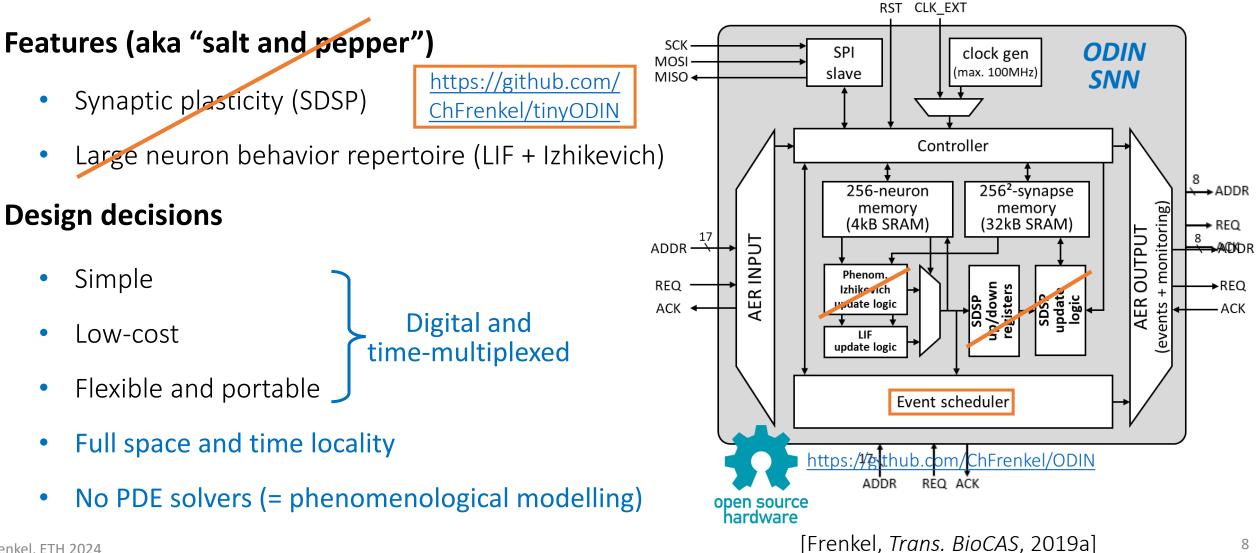

The ODIN neuromorphic chip – Architecture

Al algorithms

**Neuroscience**

ODIN is a 256x256 SNN crossbar!

Frenkel, ETH 2024

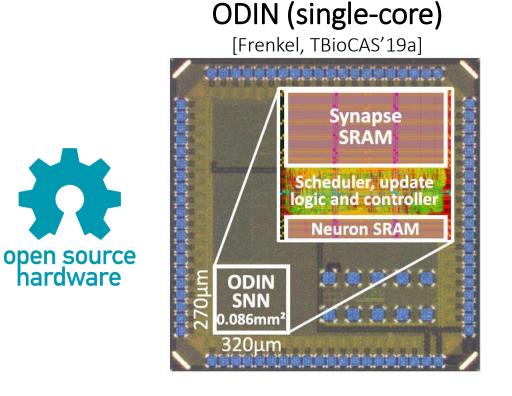

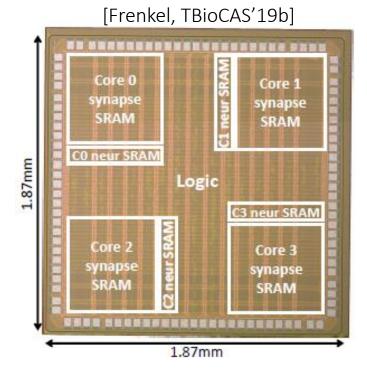

## Synaptic plasticity rules – Neuroscience as the starting point

The ODIN and MorphIC neuromorphic chips – Silicon

Neuroscience

Al algorithms

#### MorphIC (quad-core)

Record synaptic density

Energy efficiency competitive with mixed-signal designs

Large feature set (incl. 20 Izhikevich behaviors, synaptic plasticity) ...but quite painful to exploit!

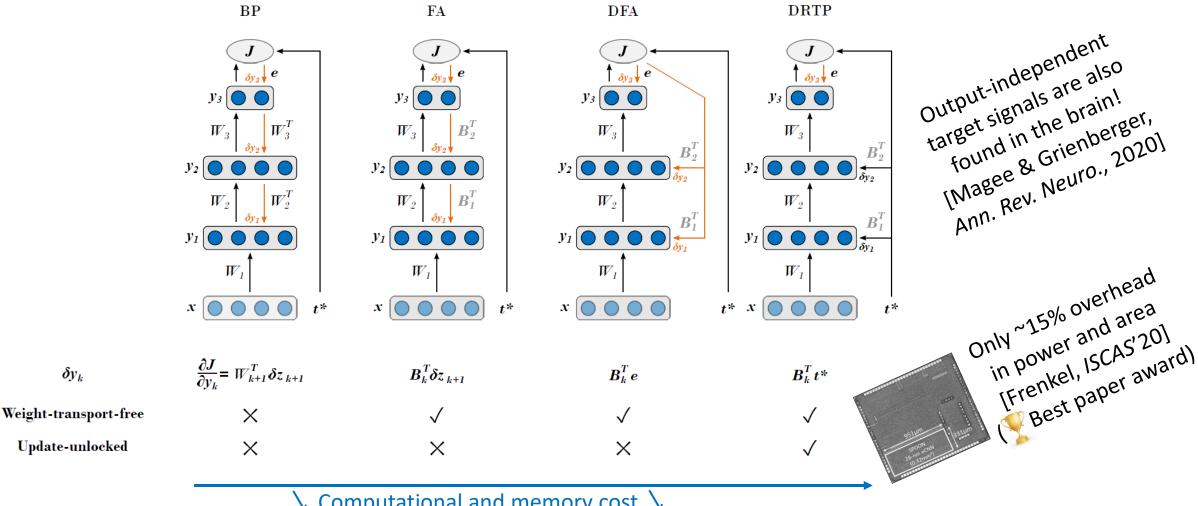

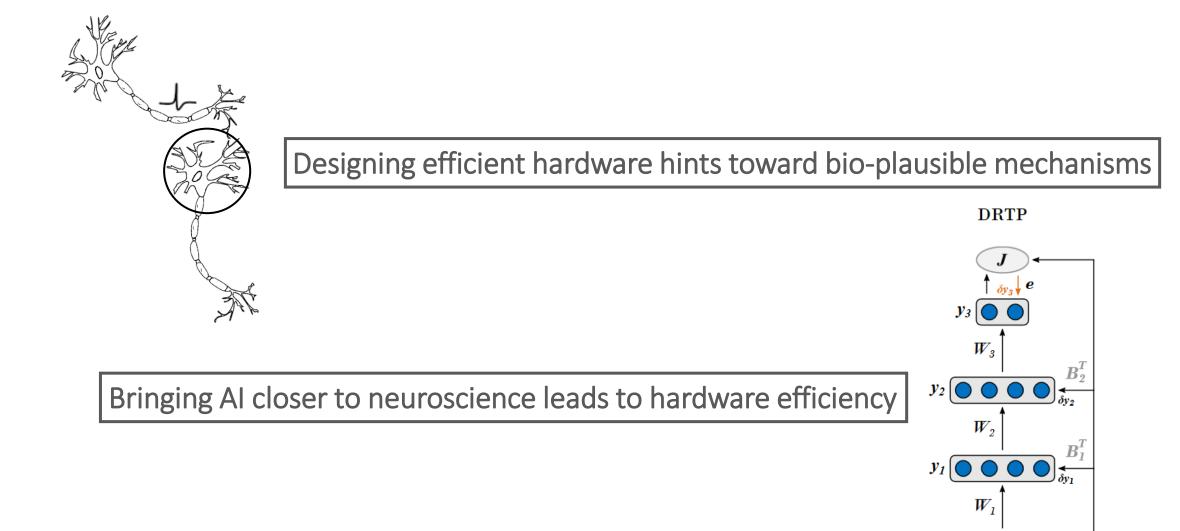

#### Neural network training – Bio-plausibility as the end goal Synergy with hardware: latency, memory access patterns

Computational and memory cost  $\searrow$

Al algorithms

**Neuroscience**

### HW efficiency and bio-plausibility are often two sides of the same coin!

Many more examples: quantization, stochastic computing, event-driven computation,...

### From neuroscience to AI and back again

Which starting point? Which perspective?

#### Outline

1 From neuroscience to AI and back again...

...which perspective? ...which starting point?

2 Why should we bother with neuroscience?

#### 3 How can we morph these questions into interesting engineering solution?

Let's use a 4-step recipe!

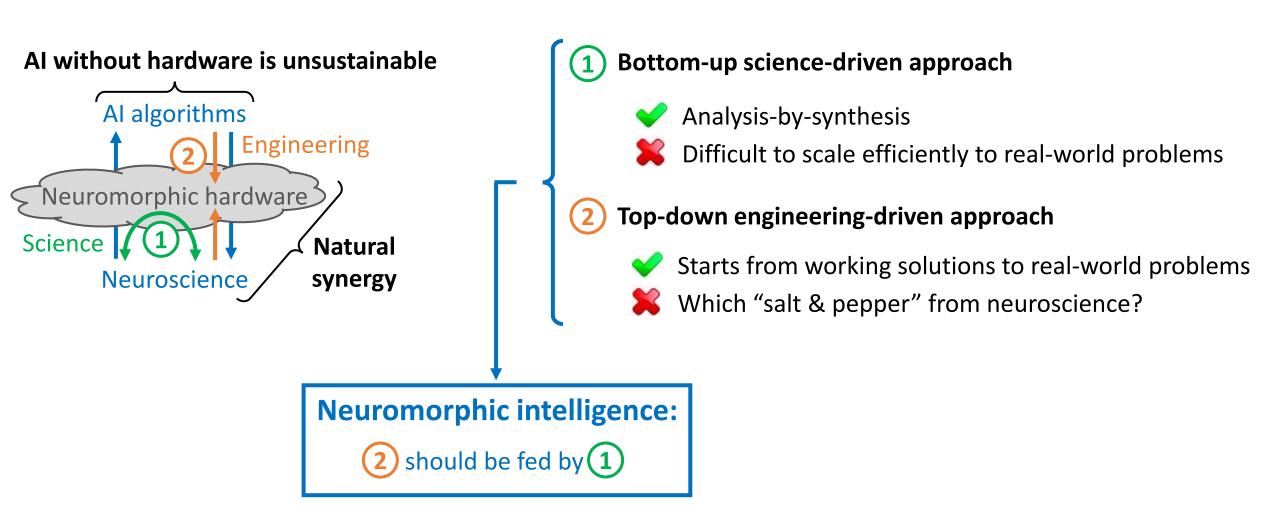

Neuromorphic intelligence:

(2) should be fed by (1)

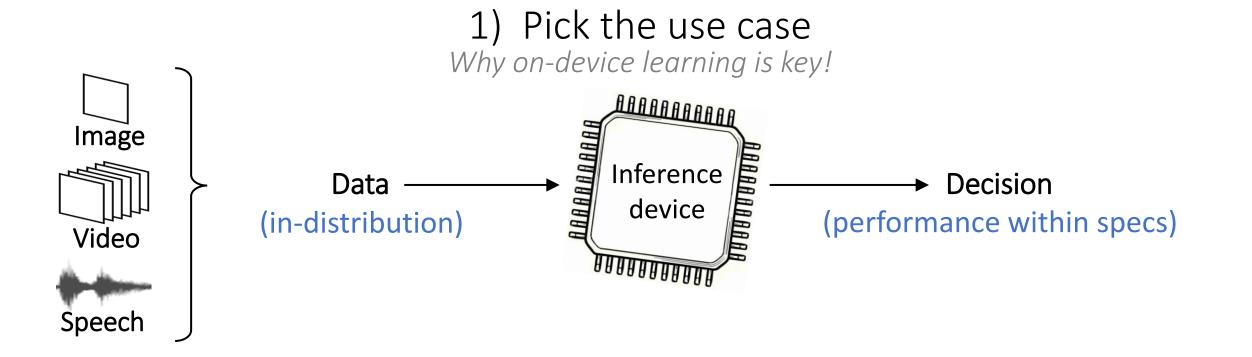

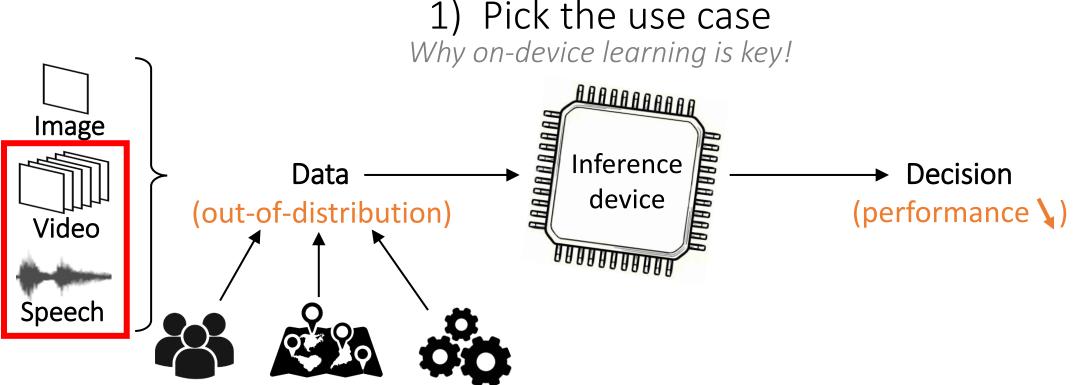

Different users, environments, task requirements

#### More training data before deployment?

Issues: cost, robustness, flexibility

#### Data exchange with the cloud?

Issues: power budget, privacy

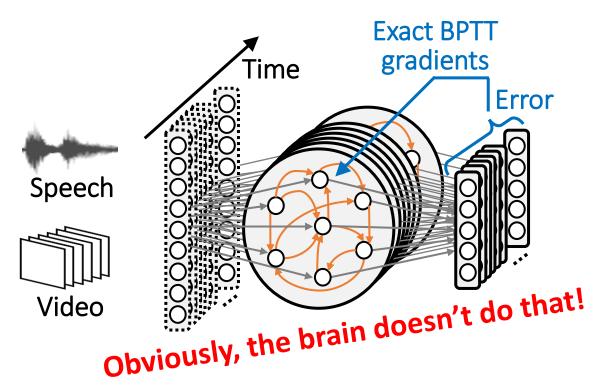

#### Why is on-chip learning over second-long timescales difficult? Let's solve a yet unsolved engineering challenge!

- Unrolling in time: very deep network (current learning ICs for static stimuli: ≤3 layers)

- Intractable memory/latency requirements

- No end-to-end on-chip solution to date

<u>Key challenge</u>: On-chip learning over long timescales while keeping a fine-grained temporal resolution

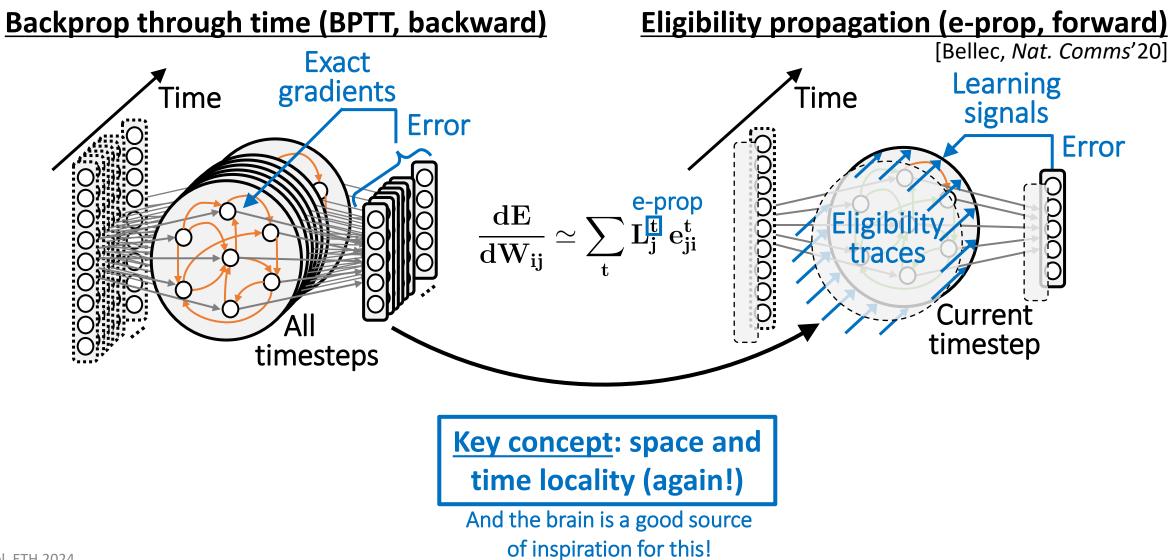

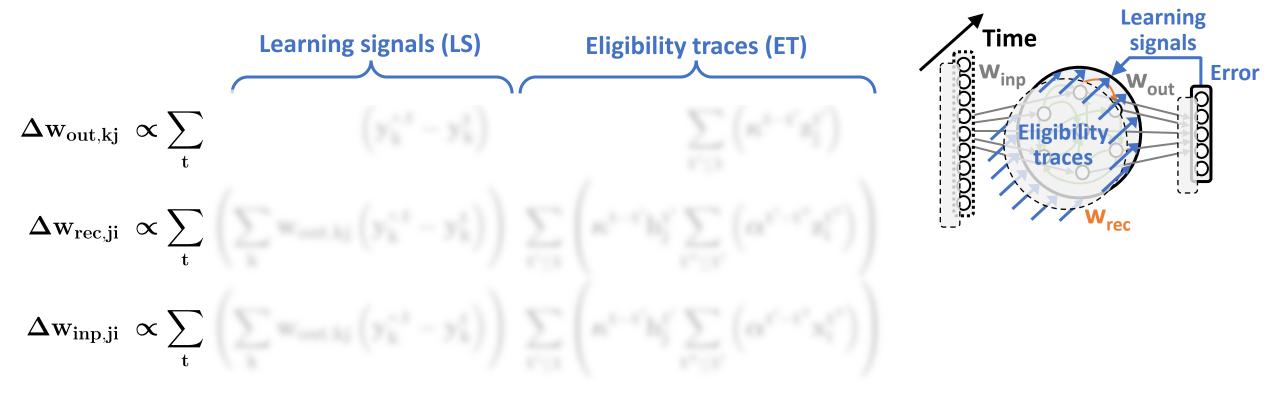

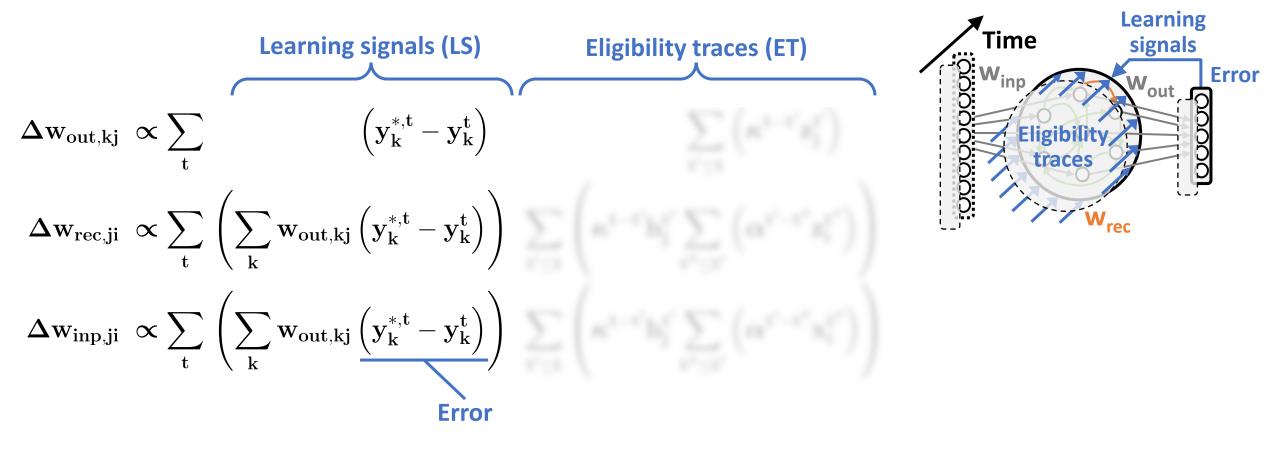

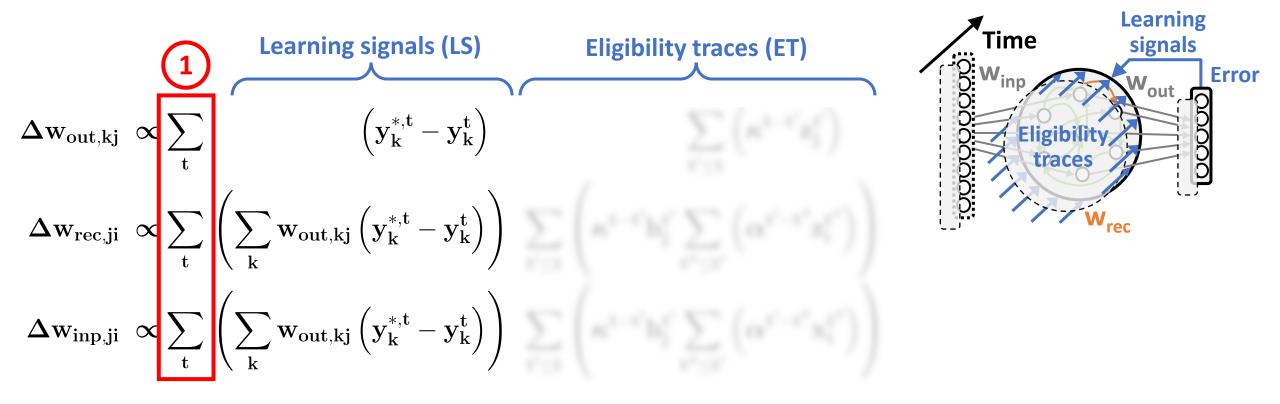

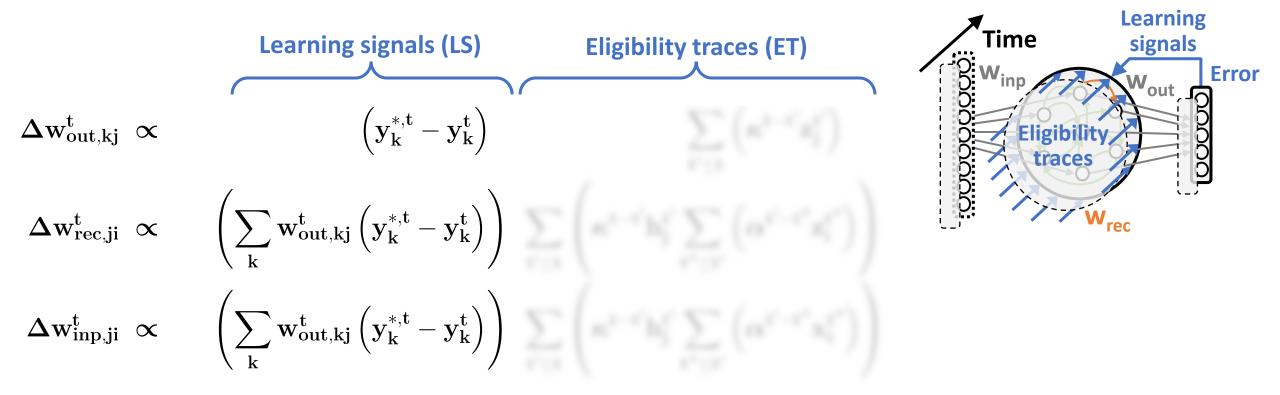

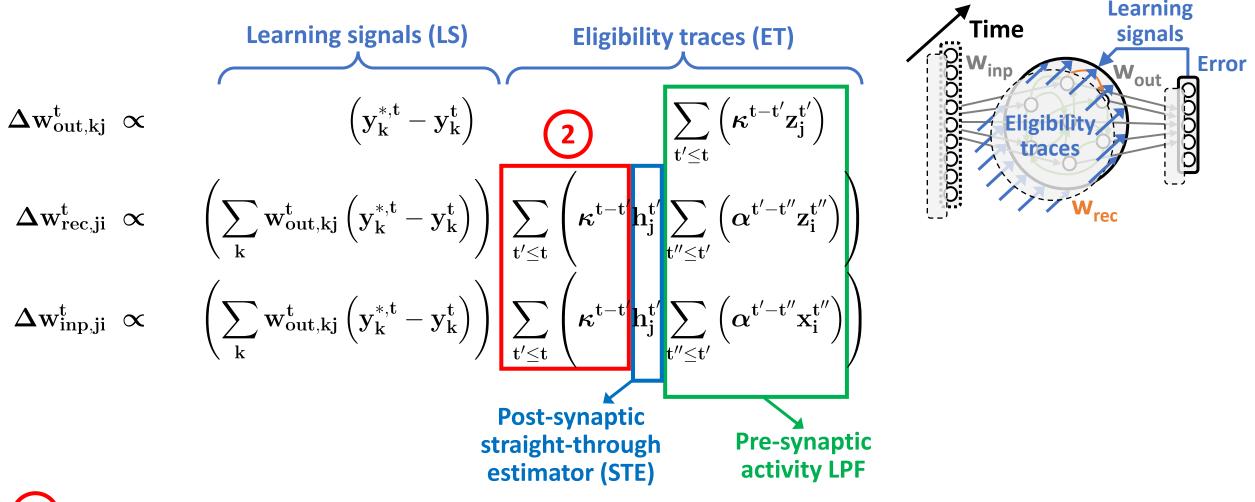

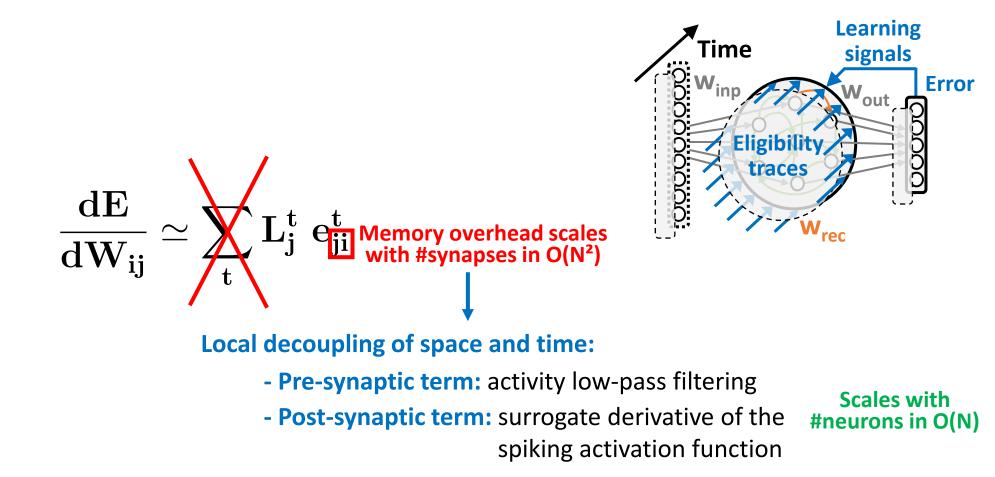

# 2) Select the (ML-informed) starting point

From BPTT to biologically plausible training

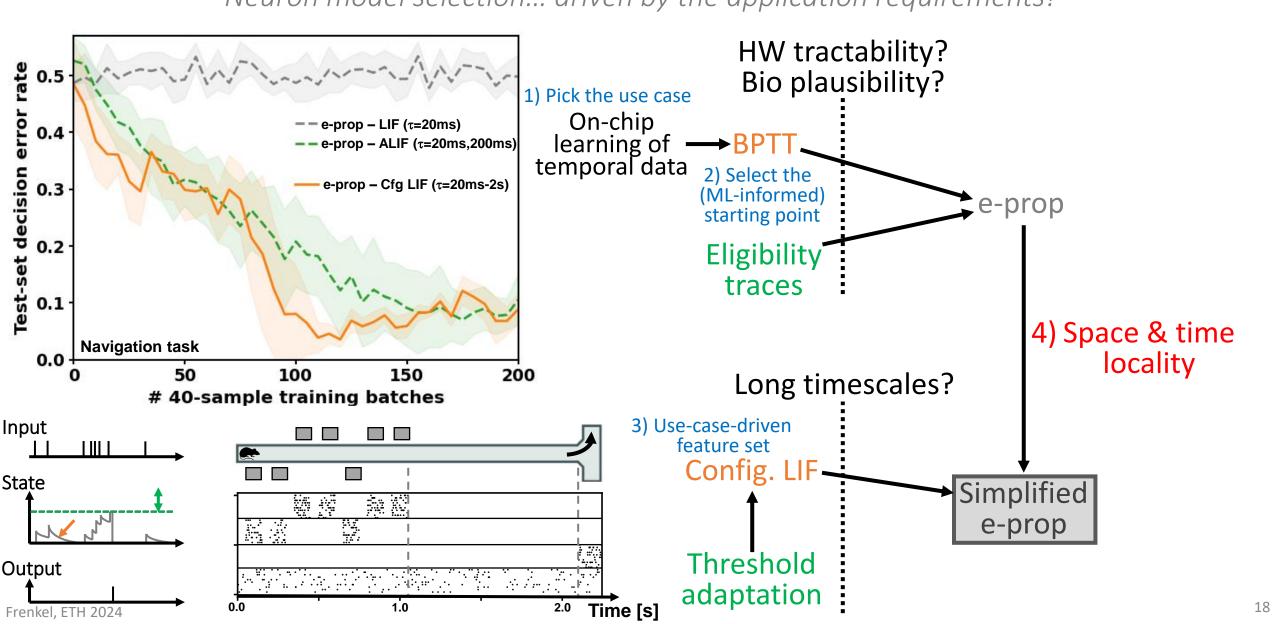

#### 3) Use-case-driven feature set selection Neuron model selection... driven by the application requirements!

*Key steps to minimize memory requirements*

*Key steps to minimize memory requirements*

*Key steps to minimize memory requirements*

Requires a dedicated gradient memory —— Per-timestep updates

*Key steps to minimize memory requirements*

*Key steps to minimize memory requirements*

Temporal coupling of pre- and post-synaptic terms — Can be neglected

Key steps to minimize memory requirements

Stochastic weight updates allow reducing weight resolution to 8 bits

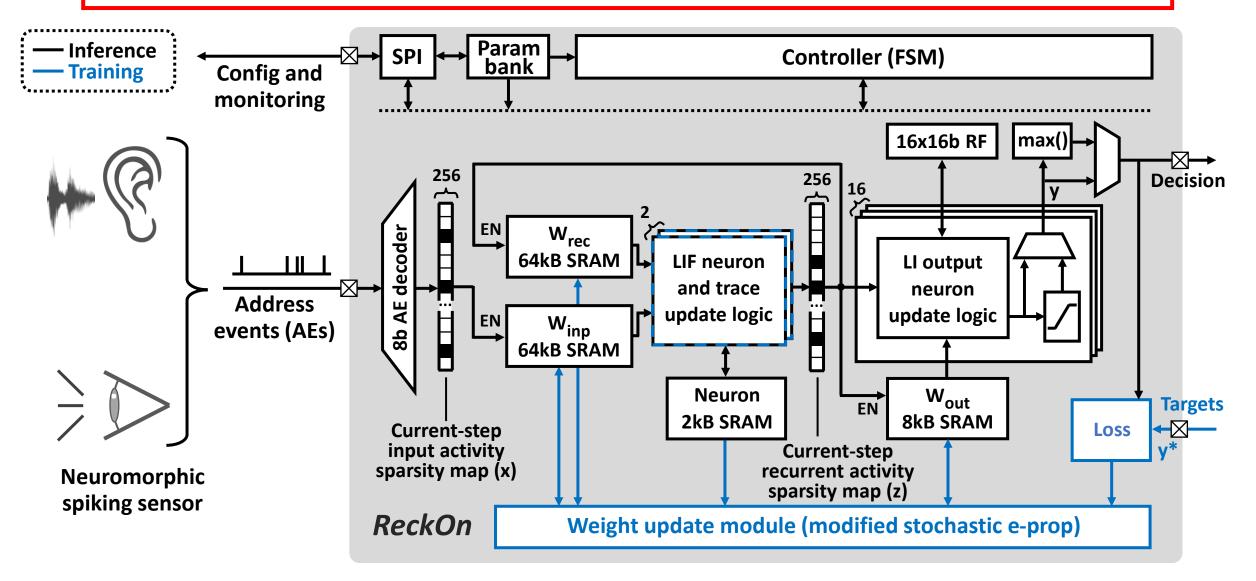

#### The ReckOn neuromorphic chip – Architecture

Same recipe as for ODIN: time multiplexing, no PDE solver, space and time locality

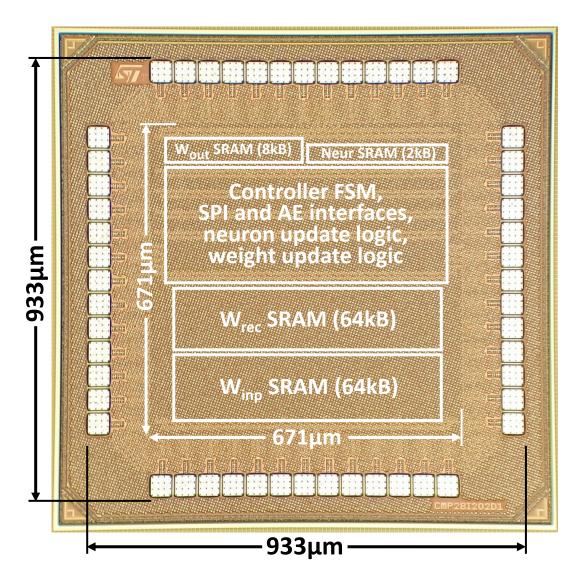

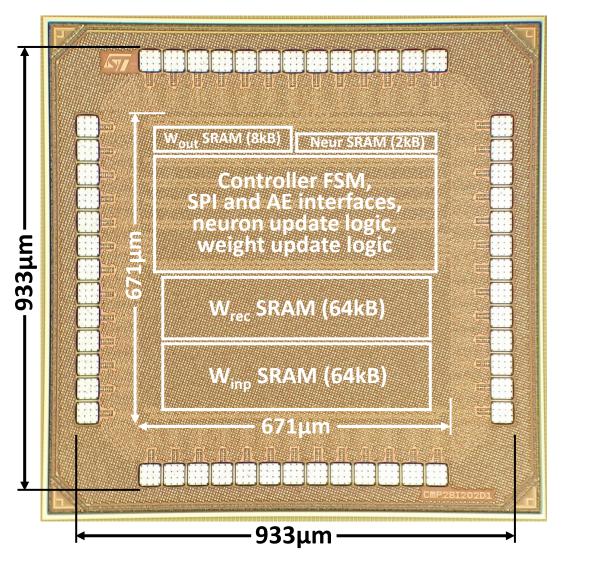

## The ReckOn neuromorphic chip – Microphotograph and summary

#### ETH

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

| Technology        | 28nm FDSOI CMOS             |           |                     |      |

|-------------------|-----------------------------|-----------|---------------------|------|

| Core size         | 0.67 x (                    | 0.67 mm²  | 0.45mm <sup>2</sup> |      |

| Die size          | 0.93 x 0.93 mm <sup>2</sup> |           |                     |      |

| SRAM              | 13                          | 38kB 🕇 🖊  | kB ext. D           | RAM! |

| Network           | Spikiı                      | ng RNN    |                     |      |

| Training timespan | Max. 3                      | 32k steps |                     |      |

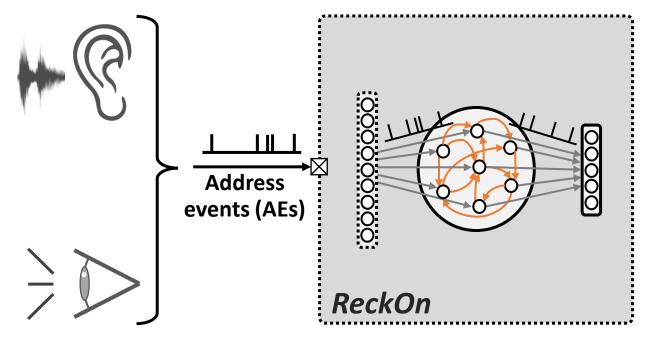

## The ReckOn neuromorphic chip – Key advantage of using spikes

- Event-driven / sparsity-aware computation

- Sensor-agnostic raw-data processing

- Task-agnostic processing and learning

Neuromorphic spiking sensor

[Frenkel, *ISSCC*, 2022]

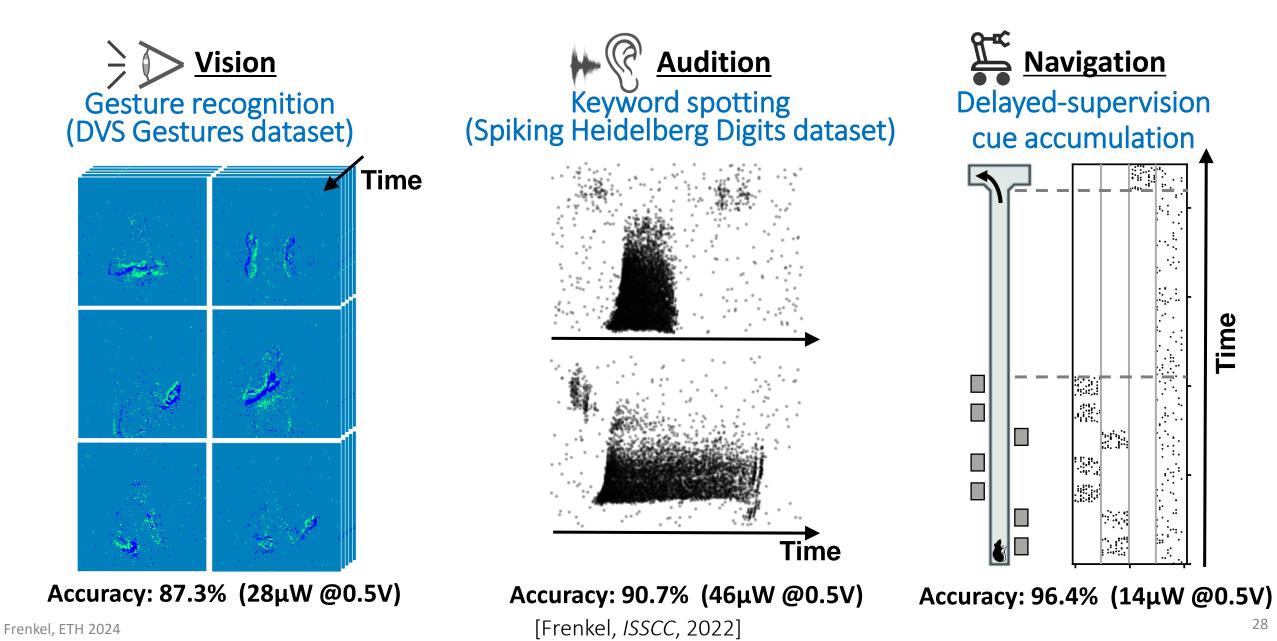

#### The ReckOn neuromorphic chip – Benchmarking

#### What you should remember

*Key elements for a competitive advantage with neuromorphic edge intelligence*

Merging AI, neuroscience and hardware is key to

achieve end-to-end on-chip learning over second-long timescales while keeping a milli-second temporal resolution, a yet unsolved challenge,

provide a low-cost solution: 0.45-mm<sup>2</sup> core area, <50µW for real-time training @0.5V,

demonstrate task-agnostic learning with a spike-based encoding toward user customization and chip repurposing at the edge.

This outlines an exciting future for neuromorphic edge intelligence!

...But wait, it's not over!

Time for yet-unpublished stuff!

#### The Cognitive Sensor Nodes and Systems (CogSys) Team

We bridge the bottom-up (bio-inspired) and top-down (engineering-driven) design approaches toward neuromorphic intelligence.

@C\_Frenkel

cfrenkel ChFrenkel R<sup>6</sup>Charlotte-FrenkelCharlotte-Frenkelc.frenkel@tudelft.nlchfrenkel.github.io

Main references:

- ODIN: [C. Frenkel et al., "A 0.086-mm<sup>2</sup> 12.7-pJ/SOP 64k-synapse 256-neuron onlinelearning digital spiking neuromorphic processor in 28nm CMOS," *IEEE Trans. BioCAS*, 2019]

Questions?

- MorphIC: [C. Frenkel et al. "MorphIC: A 65-nm 738k-synapse/mm<sup>2</sup> quad-core binary-weight digital neuromorphic processor with stochastic spike-driven online learning," *IEEE Trans. BioCAS*, 2019]

- DRTP: [C. Frenkel, M. Lefebvre et al., "Learning without feedback: Fixed random learning signals allow for feedforward training of deep neural networks," *Frontiers in Neuroscience*, 2021]

- SPOON: [C. Frenkel et al., "A 28-nm convolutional neuromorphic processor enabling online learning with spike-based retinas," *IEEE ISCAS*, 2020]

- **Review:** [C. Frenkel, D. Bol and G. Indiveri, "Bottom-up and top-down approaches for the design of neuromorphic processing systems: Tradeoffs and synergies between natural and artificial intelligence," *Proceedings of the IEEE*, 2023]

- **ReckOn:** [C. Frenkel and G. Indiveri, "ReckOn: A 28-nm Sub-mm<sup>2</sup> Task-Agnostic Spiking Recurrent Neural Network Processor Enabling On-Chip Learning over Second-Long Timescales," *IEEE International Solid-State Circuits Conference (ISSCC)*, 2022]

*Open-sourced!* github.com/ChFrenkel/ODIN

*Open-sourced!* <u>github.com/ChFrenkel/Direct</u> <u>RandomTargetProjection</u>

*Open-sourced!* github.com/ChFrenkel/ReckOn