Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich Integrated Systems Laboratory Microelectronics Design Center

# **Research Review 2005**

### Cover Image: Atomistic Simulations in Nanoelectronic Technologies

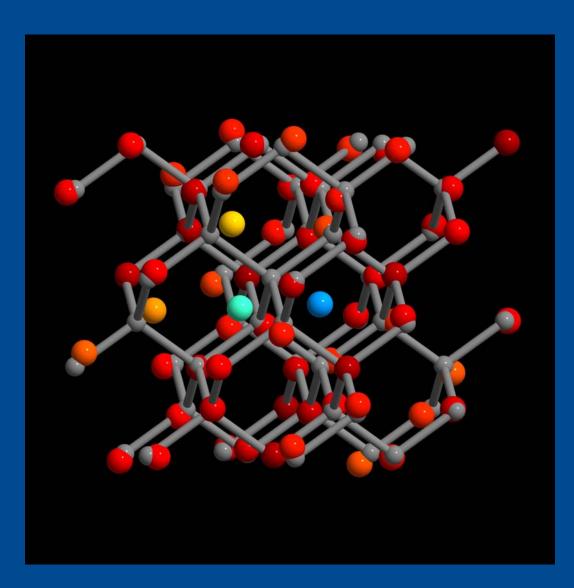

The picture on the cover is a freeze image of an *ab initio* molecular dynamics simulation of the self-interstitial defect in silicon. The silicon atoms are colored according to their distance to the closest lattice site of a reference lattice, shown in grey. The two atoms with the largest distance are part of the defect.

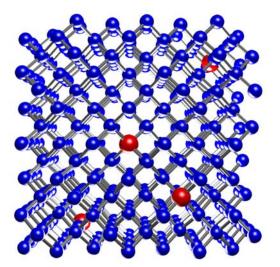

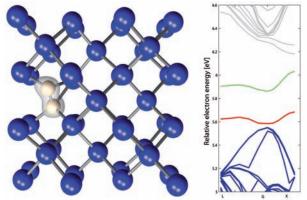

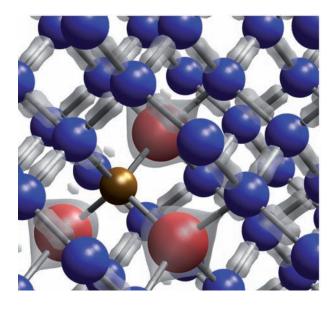

Simulation setup: A super cell containing 216 atoms for atomistic *ab initio* computer simulations. Red spheres represent arsenic dopants, blue spheres are Si host atoms.

One of the consequences of the ongoing miniaturization in semiconductor technology is that standard process simulation tools based on continuum models cannot provide accurate and predictive results for such small geometries. Therefore, the understanding and physics-based simulation of the devices require a simulation paradigm change to the atomistic realm. Moreover, advanced and future technologies need to use new materials. These material systems have to be investigated by atomistic simulations

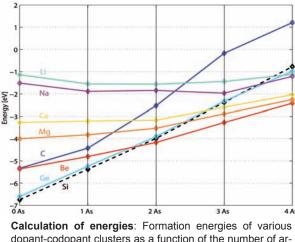

dopant-codopant clusters as a function of the number of arsenic atoms involved.

Address of the Laboratory:

ETH Zürich Integrated Systems Laboratory ETZ J81 and J96 Gloriastr. 35 8092 Zurich, Switzerland

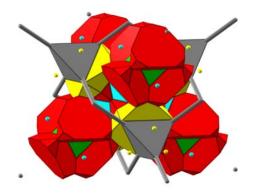

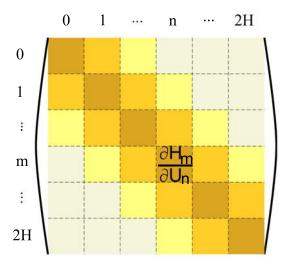

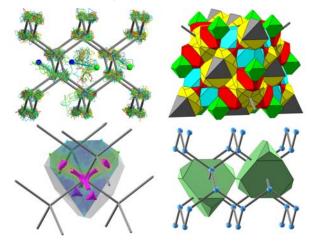

**Post processing of first principles calculations:** Evaluation of different silicon interstitial configurations by means of a Voronoi cell analysis in the diamond lattice.

in order to improve insight view and performance of such technologies. The investigation of these new compounds by simulations on the atomistic level is a prerequisite for the optimization of the new technologies.

Ab initio simulations based on Density Functional Theory (DFT) allow for the examination of band structures, electrical and magnetic properties, as well as binding energies and migration energy barriers of atomic processes. In addition, molecular dynamics DFT simulations are performed in order to evaluate diffusion mechanisms and diffusion constants for defects and dopants in a host material. Most of the atomistic parameters calculated this way are inaccessible to direct experimental measurements and therefore provide invaluable information for the understanding and development of new technologies. The projects involved in atomistic simulations are focusing on the study of point defect diffusion and electrical donor deactivation in silicon. Also, the behavior of light alkali and alkaline earth metals in conjunction with n-type silicon doping is investigated. Further information can be found on pages 58 (right) and 59.

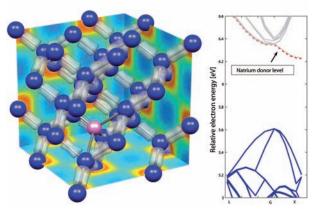

**Electronic structure calculation**: The two carbon impurities in a  $C_i C_s$  defect (white spheres) form a defect pair with two strongly localized donor levels (grey electron cloud and red band in the bandstructure plot). Moreover, the carbon pair can act as an electron acceptor (green line).

| Phone:               | +41 44 632 42 68                              |

|----------------------|-----------------------------------------------|

| Fax:                 | +41 44 632 11 94                              |

| e-mail:              | sekr@iis.ee.ethz.ch                           |

| WWW:                 | http://www.iis.ee.ethz.ch                     |

| Visitor information: | $\rightarrow$ contacts $\rightarrow$ visitors |

Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich Integrated Systems Laboratory Microelectronics Design Center

# **Research Review 2005**

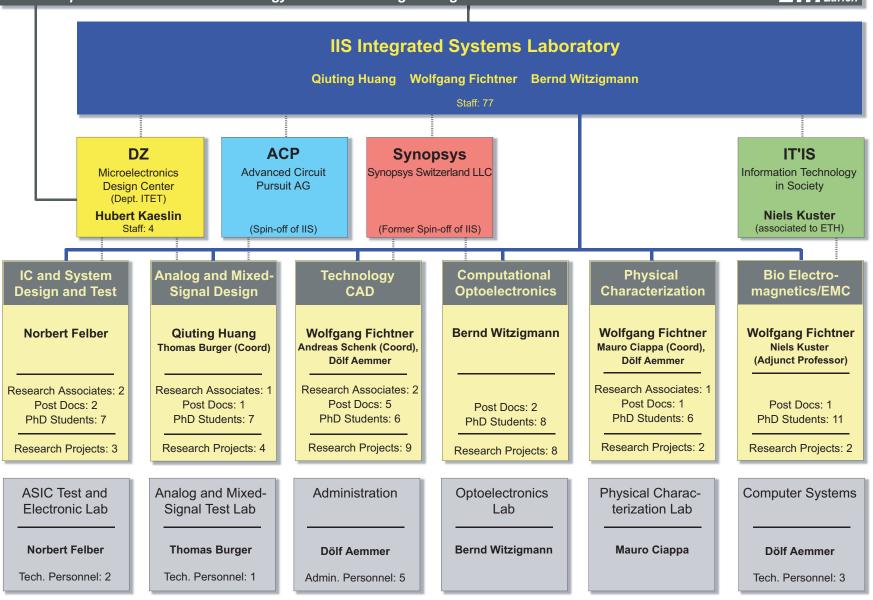

| Qiuting Huang  | Wolfgang Fichtner |                | Bernd Witzigmann |

|----------------|-------------------|----------------|------------------|

| Hubert Kaeslin |                   | Norbert Felber | Dölf Aemmer      |

## Hyperthermia Treatment Planning

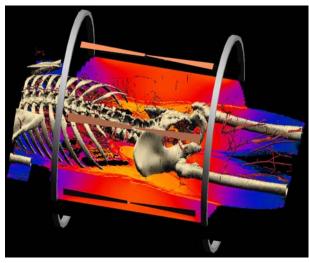

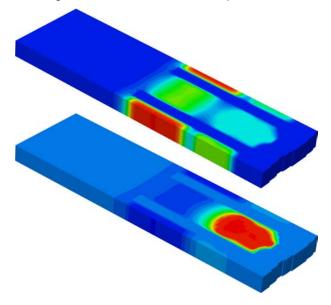

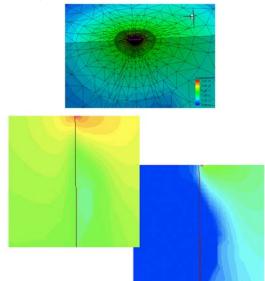

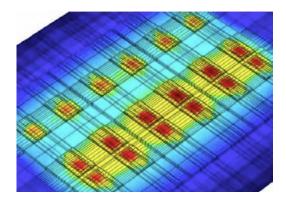

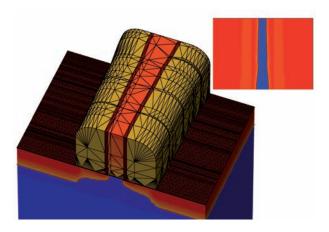

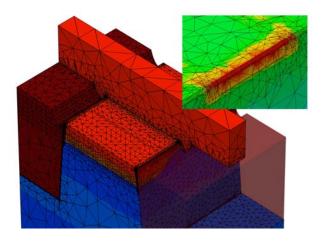

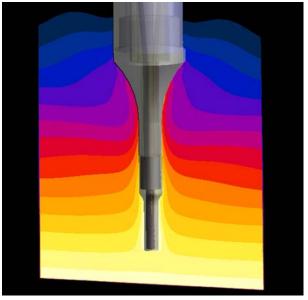

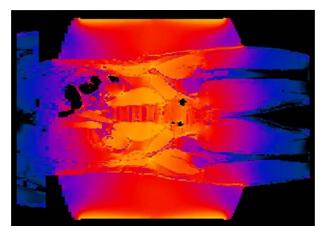

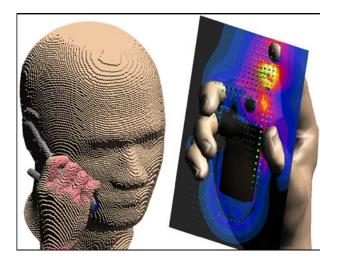

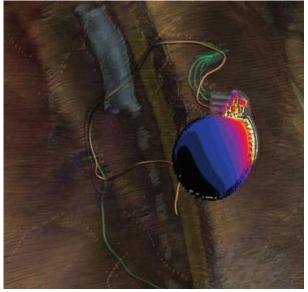

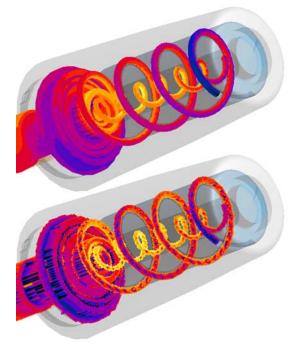

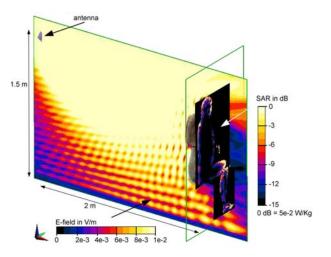

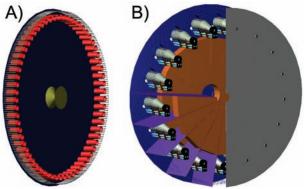

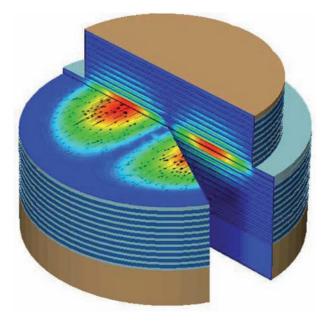

EM Simulation of SAR (specific absorption rate) distribution induced by a Sigma-60 hyperthermia applicator.

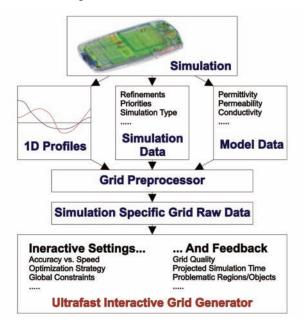

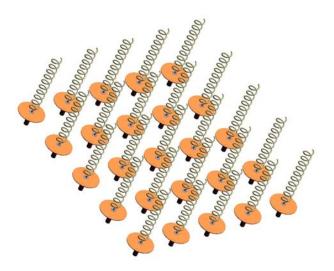

Currently a comprehensive *Hyperthermia Treatment Planning* (HTP) tool is being developed. It is based on the existing electro-magnetism (EM) simulation platform *SEMCAD X*. Hyperthermia is a treatment modality for cancer that can strongly increase survival rates. It consists of heating the tumor to a temperature that should ideally lie above 43 °C. This goal is usually achieved by exposing the patient to EM radiation. Often, an antenna-array is used to achieve the desired deposition pattern.

In order to increase the treatment quality and efficiency, a patient based planning tool is required. This software will perform the following main tasks:

- Transform medical imaging data into a model of the patient on which simulations can be carried out.

- Simulate the EM field distributions generated by the different antennas.

- Predict the resulting temperature increase in the patient, taking into account blood flow and specific heat generation rates of the various tissues.

- Optimize the amplitudes and relative phases of the various antennas to obtain the 'best' configuration.

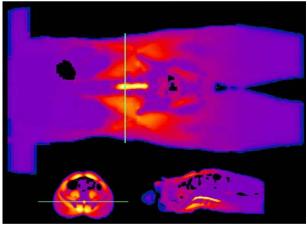

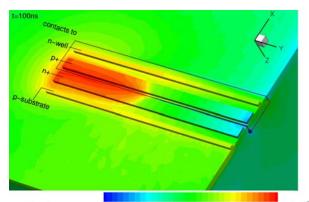

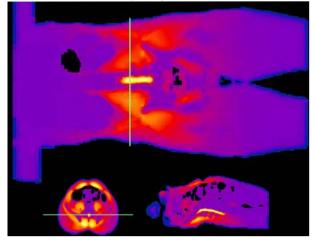

The corresponding temperature distribution as obtained based on the Pennes Bioheat Equation.

Detailed applicator models have been constructed which has then been used to carry out initial calculations using the *SEMCAD X* software. Some requirements for the EM

and temperature simulation have been specified, and problematic areas could be identified. The influence of some parameters (e.g., temperature of surrounding water bolus) has been studied.

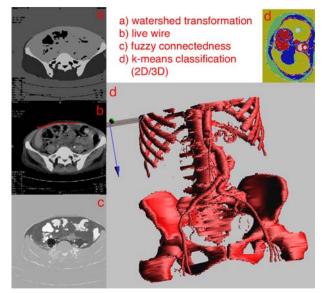

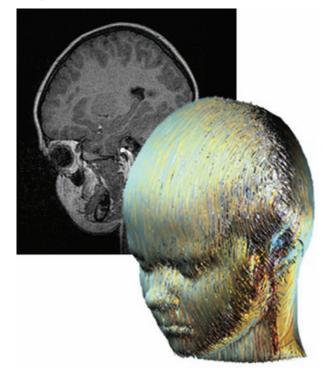

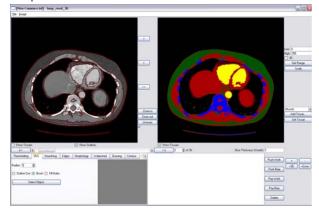

A flexible image segmentation toolbox has been created that permits fast, robust image segmentation. It is complemented by a front-end that supports a large range of possible user interactions and has been designed to blend a large amount of information into intuitive views.

A new model for the influence of blood vessels on the heat distribution is being developed. It is based on tensorial heat conduction and connecting the simulation to a pseudo 1D-simulation of heat transport in the vessel network. Furthermore, a code is being written that permits temperature dependent tissue parameters.

The software will eventually be helpful in developing new applicators as well.

Results obtained using some segmentation methods offered by the segmentation tool box.

The goal is a comprehensive software package that covers all steps from developing applicators to simulating the EM fields they induce, obtaining the resulting temperature distributions, and calculating the optimal steering parameters to get the best possible treatment.

More information can be found on pages 82 (right) and 83.

## Contents

| Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                                                                                                                    |

| Representative Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                                                                                                                    |

| Staff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                                                                                                                    |

| Former PhD Students                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16                                                                                                                    |

| Academic Guests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20                                                                                                                    |

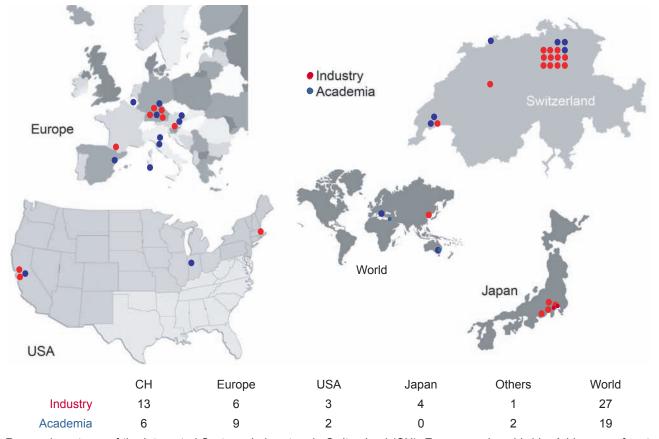

| Partners and Funding Agencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                                                                                    |

| Awards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                                                    |

| Patents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20<br>29                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                       |

| History of the Integrated Systems Laboratory (IIS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30                                                                                                                    |

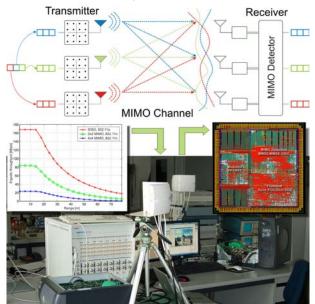

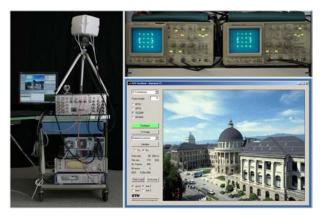

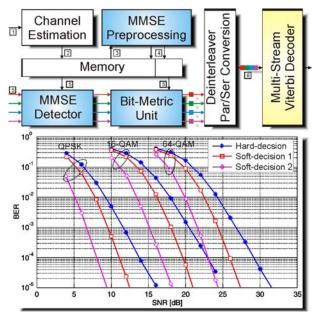

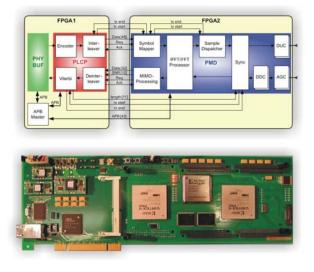

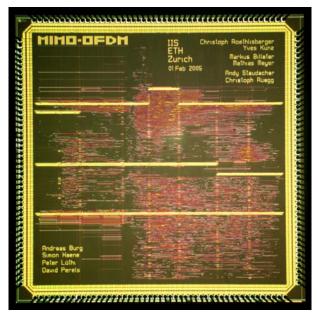

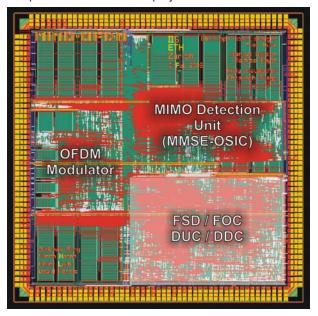

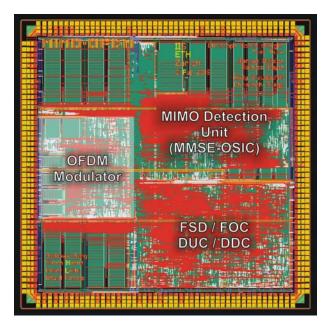

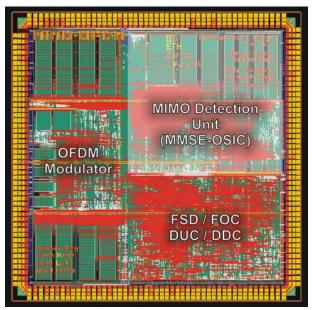

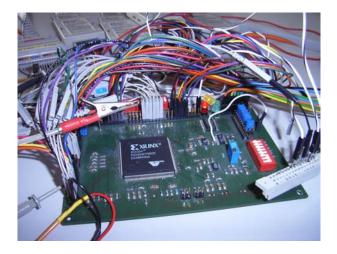

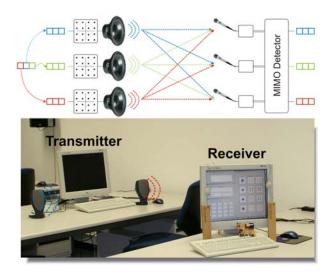

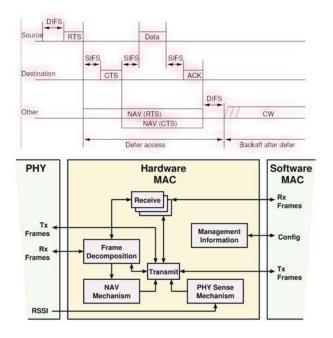

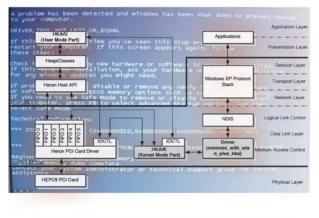

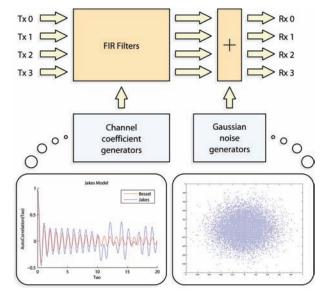

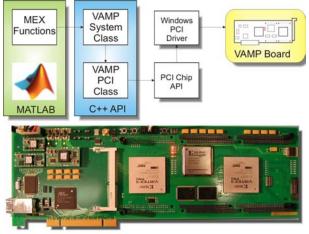

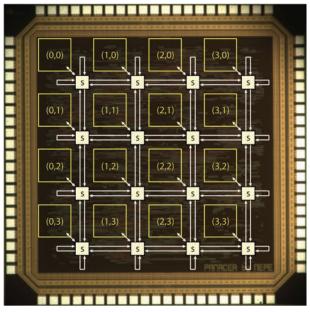

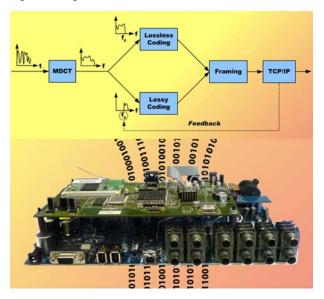

| Research Projects: IC and System Design and Test<br>Circuits and Systems for Wireless Communications<br>Real-Time MIMO-OFDM Testbed<br>MIMO Detection and Channel Decoding<br>Medium Access Control for MIMO-OFDM Testbed<br>MIMO-OFDM Transceiver Chip<br>MIMO-OFDM Transceiver Chip: Frontend<br>MIMO-OFDM Transceiver Chip: OFDM Modulator<br>MIMO-OFDM Transceiver Chip: OFDM Modulator<br>MIMO-OFDM Transceiver Chip: MMSE-OSIC Detector<br>Implementation Aspects of Pseudo-Linear MIMO Detectors<br>VLSI Implementation of Reduced-Complexity Maximum-Likelihood Algorithms for MIMO Systems<br>Sphere Decoding with Resource Constraints<br>Baseband Processing on a Reconfigurable Processor<br>MIMO-OFDM Frequency Offset Estimation<br>GALS System Design<br>Side-Channel-Attack Secure Crypto-Hardware<br>Clock Oscillator with Variable Period<br>Low-Power VLSI Implementation of Hearing Aid Algorithms<br>Adaptive Directional Microphone for Hearing Aids<br>Low-Power Speech Enhancement through Spectral Sharpening in Hearing Aids<br>A New Low-Power Multiplier for Low-Frequency Applications | <b>34</b><br>35<br>36<br>36<br>36<br>37<br>37<br>38<br>39<br>39<br>40<br>40<br>41<br>41<br>42<br>43<br>43<br>44<br>44 |

| Research Projects: Analog and Mixed-Signal Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45                                                                                                                    |

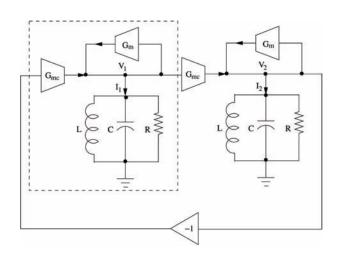

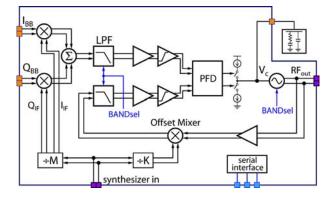

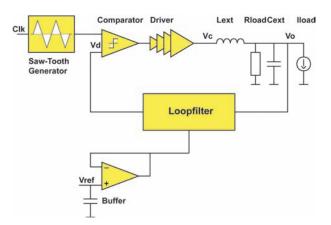

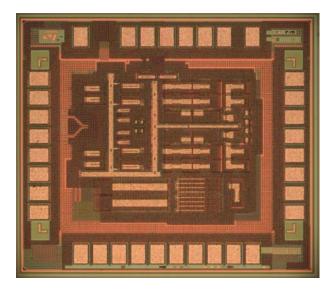

| High-Speed Pipelined A/D Converters in Deep-Submicron DMOS Technology<br>Folding and Interpolating A/D Converters in Deep Submicron Technology<br>Frequency Synthesis for Ultra-Wideband Systems<br>High Frequency Quadrature Oscillators<br>Quadrature Modulator and Transitional Loop for GSM/DCS Mobile Transmitters<br>Co-Integration of DC-DC Conterters for Systems on Chip<br>Multi-Standard RF Front-Ends for Mobile Communications<br>A/D Conversion for Multi-Standard Wireless Receivers<br>Multi-Standard Low-Power Base-Band Digital Receiver<br>Testbed for the Base-Band Signal Processing Part of a Digital Receiver<br>A Low-Power, Multi-Mode, Transmit I/Q Modulator in 0.13 µm CMOS<br>Frequency Synthesizer for a UMTS Transceiver                                                                                                                                                                                                                                                                                                                                                             | 46<br>47<br>47<br>48<br>49<br>49<br>50<br>50<br>51<br>51                                                              |

| Research Projects: Technology CAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 52                                                                                                                    |

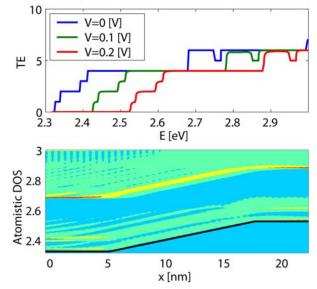

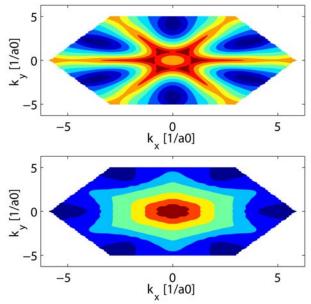

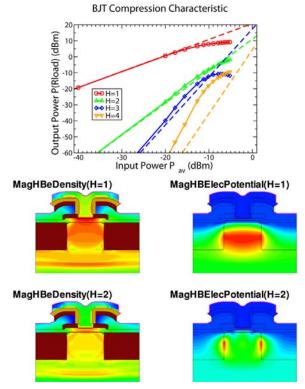

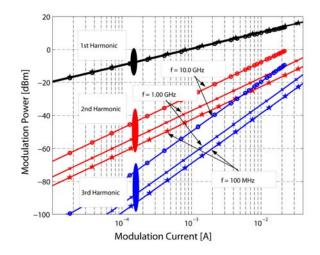

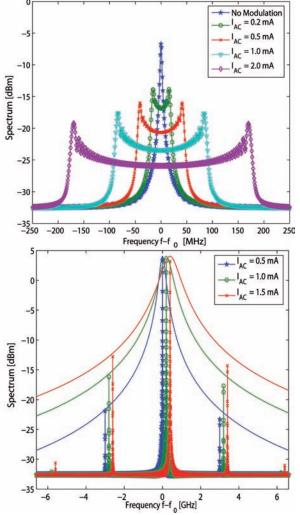

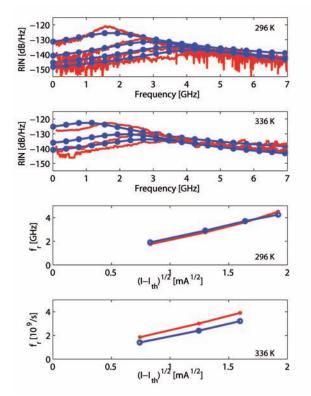

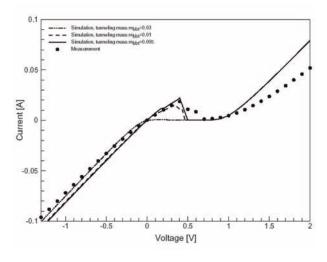

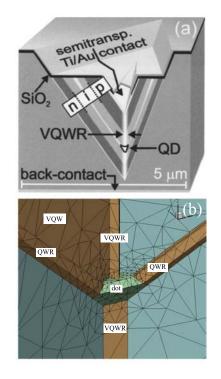

| <ul> <li>Modeling of Post-CMOS Devices</li> <li>New One-Particle Monte Carlo Method</li> <li>Full-Band Formalism in Quantum Transport Modeling</li> <li>Scattering in Nanoscale Devices</li> <li>Rigorous Treatment of Coupled Modes in the NEGF Formalism</li> <li>Atomistic Simulation of Quantum Wire Based Transistors</li> <li>Application of the sp3d5s* Tight-Binding Method for the Bandstructure of Bulk, Quantum Well, and Quantum Wire</li> <li>The Harmonic Balance Approach in the Simulation of Semiconductor Devices</li> <li>Physics-Based Characterization of RF Transistors by Means of Harmonic Balance Simulations</li> <li>Harmonic Distortion in Quantum Well Edge-Emitting Lasers</li> <li>Robust and Efficient Solving Strategies for the Nonlinear One-Tone Harmonic Balance Equation</li> </ul>                                                                                                                                                                                                                                                                                           | 53<br>54<br>54<br>55<br>55<br>56<br>56<br>57<br>57<br>58                                                              |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | Electrical Behavior of Alkali and Alkaline Earth Metals in Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59<br>59 |

|      | Improvement of Diffusion and Activation Models by Ab Initio Simulations<br>Robust Iterative Solvers in Nanoelectronic Computational Science                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59<br>60 |

|      | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60       |

| Doco |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61       |

| rese | <b>,</b> , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62<br>62 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63       |

|      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65<br>65 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68<br>68 |

| _    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| Rese |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69       |

|      | a sub-server the server ser | 70       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70<br>71 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73       |

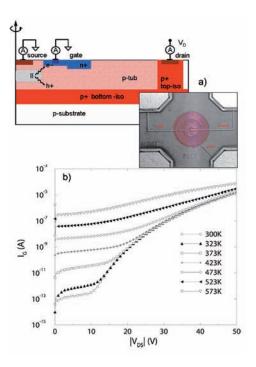

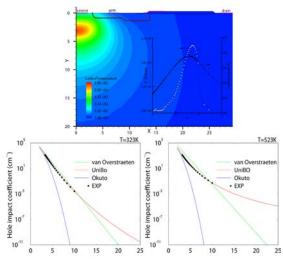

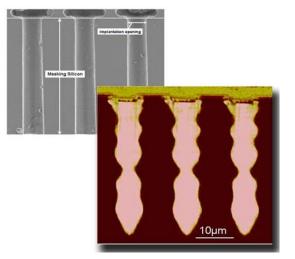

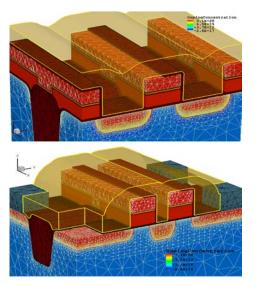

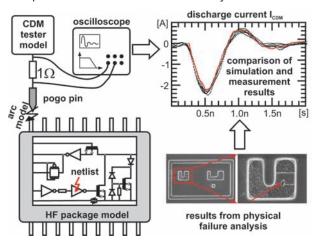

|      | Performance and Limitations in Accurate Electrothermal Compact Modeling of Power Modules<br>3D Device Simulation of Thyristors as CMOS ESD Protection Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73<br>74 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74       |

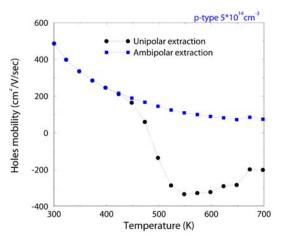

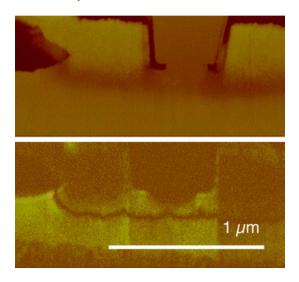

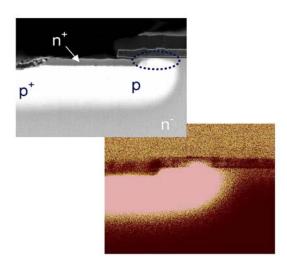

|      | 2D Dopant Profiling of SiC MOSFET Devices by Scanning Capacitance and Secondary Electron Dopant Contrast                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75       |

|      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76       |

|      | 5 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 76<br>77 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77       |

|      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 78       |

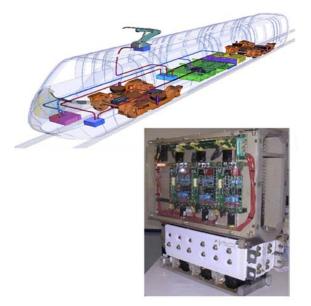

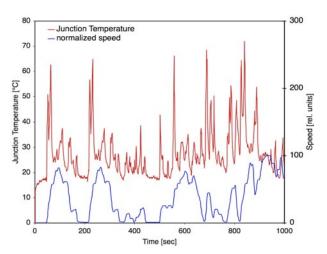

|      | Lifetime Prediction of Power Devices on the Base of Mission Profiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 78       |

| Rese | arch Projects: Bio-Electromagnetics and Electromagnetic Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79       |

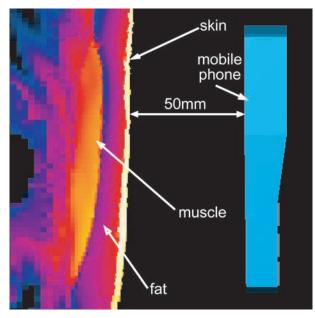

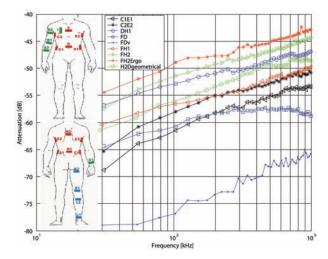

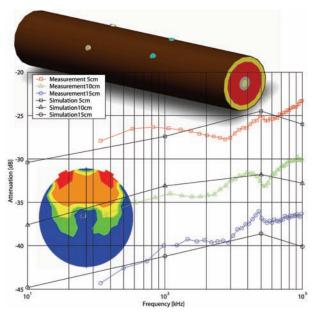

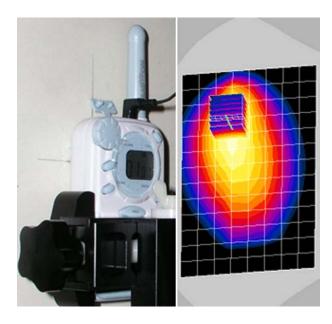

|      | SAR Assessment in Layered Body Tissue in the Near- and Far-Field of Wireless Body Worn Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 81<br>82 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83       |

|      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 83       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84<br>85 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87<br>88 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89       |

|      | Study of UMTS Base Station Like Exposure in Well Being and Cognitive Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 89       |

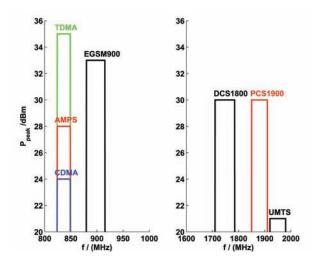

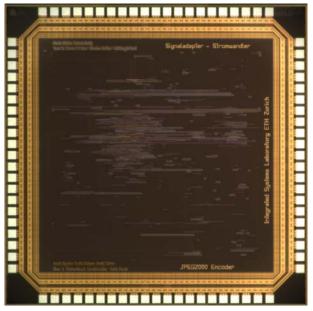

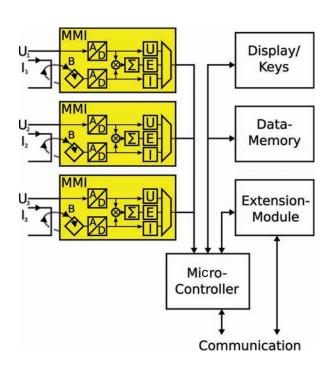

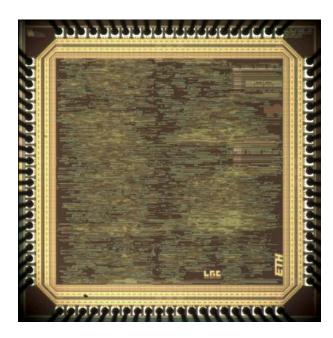

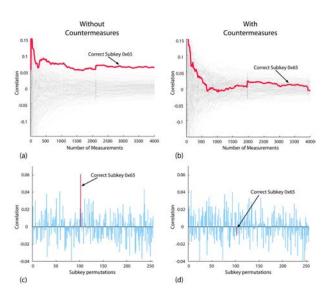

|      | Rodent Toxicity/Carcenogenicity Studies on Cell Phone Radio Frequency Radiation in Reverberation Chambers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |