Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

# Network-enabled digital lock box for trapped-ion experiments QuanTech Workshop

G. Bisson, M. Glantschnig, D. Hagmann, P. Tirler

## Sunday 15th May, 2022

#### Abstract

Experiments with trapped ions require lasers which are stable in frequency, amplitude and phase. To achieve this, one commonly uses active feedback, i.e. one measures the deviation of a quantity from its desired value and feeds this error back to the system. To tune this feedback loop, one commonly uses a PID (Proportional, Integral, Derivative) controller, which is also referred to as a lock box.

The aim of this QuanTech project was to develop a replacement for the digital lock box *EVIL* that had been used at the Trapped Ion Quantum Information group over the past decade and which has become deprecated since. We evaluated different options and eventually opted for a semi-custom solution based on the commercial mixed signal Red Pitaya STEMlab 125-14 board. Special care was taken to ensure backward compatibility with the previous solution, both hardware and software wise.

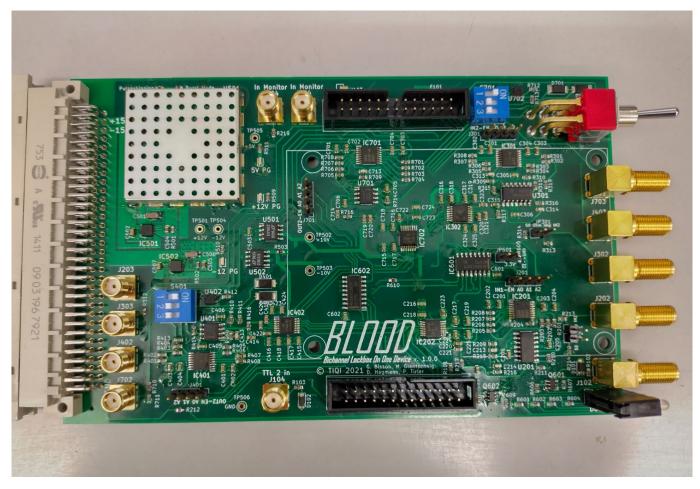

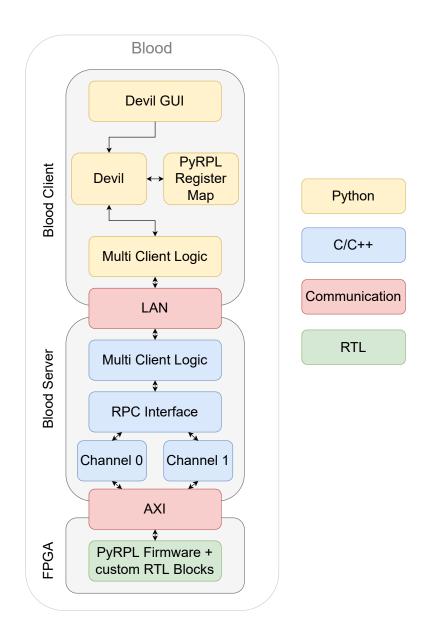

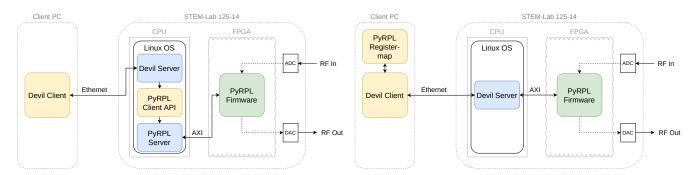

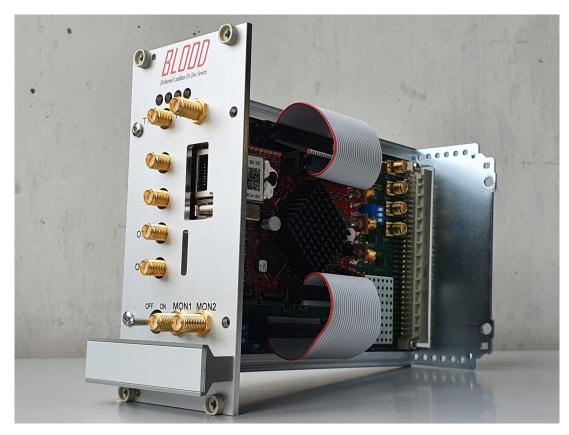

To this end, we designed a custom printed circuit board which we called *Bichannel Lockbox On One Device (BLOOD)* that can be deployed in the same Eurocard racks that are used for the EVIL, i.e. has the same form factor and power supplies. This PCB also comes with the possibility to change the gain and offset of the analog inputs and outputs digitally. It runs custom software, for which we combined the open-source *PyRPL* project, a software/firmware stack designed for controlling AMO experiments on the Red Pitaya with Python, with *DEVIL*, the software currently used to control the EVILs in the TIQI group.

During the course of this project we built a prototype of the BLOOD and we verified that the softand hardware work together in the way we intended. However, to make it fully usable in the lab, some further improvements are needed.

## Acknowledgements

We want to thank Prof. Jonathan Home and the whole Trapped Ion Quantum Information (TIQI) group at ETH for the opportunity we had to join their group for this project. In particular, we want to thank our supervisors Martin Stadler, Nick Schwegler and Vlad Negnevitsky for their close support in planning and execution throughout the project, without which this would not have been possible. We also owe thanks to all other group members who helped us throughout the last semester, including, among others, Peter Clements, Matt Grau, Ilia Sergachev and Robin Oswald.

# Contents

| 1  | oduction                                    | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|----|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| T  | 1.1                                         | Control in Trapped-Ion experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5      |

|    |                                             | 1.1.1    The PDH lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5      |

|    | 1.2                                         | State of the Art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6      |

|    |                                             | 1.2.1 Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6      |

|    |                                             | 1.2.2 Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6      |

|    | 1.3                                         | Reason for upgrade                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6      |

|    | 1.4                                         | Project goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6      |

| 2  | Evo                                         | cution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8      |

| 2  | <b>Exec</b> 2.1                             | The Printed Circuit Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8<br>8 |

|    | 2.1                                         | 2.1.1      Schematics      Schematics </td <td>8<br/>8</td> | 8<br>8 |

|    |                                             | 2.1.2 Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13     |

|    |                                             | 2.1.2 Edyout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13     |

|    | 2.2                                         | Software/Firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14     |

|    | 2.2                                         | 2.2.1 Testing of PyRPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14     |

|    |                                             | 2.2.2 Software-Firmware Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17     |

|    |                                             | 2.2.3 Adaptation of the PyRPL Firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17     |

|    |                                             | 2.2.4 Modified pyrpl_tiqi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18     |

|    |                                             | 1.3 F 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19     |

|    |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20     |

|    |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| 3  | Resu                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22     |

|    | 3.1                                         | Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22     |

|    | 3.2                                         | PCB Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22     |

|    |                                             | 3.2.1 Input & Output Sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23     |

|    |                                             | 3.2.2 Communication between RedPitaya and ICs on the PCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24     |

|    | 3.3                                         | Open-loop transfer function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24     |

|    | 3.4                                         | PDH lock of laser to a cavity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25     |

|    | 3.5                                         | Outlook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27     |

|    |                                             | 3.5.1 Open issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27     |

|    |                                             | 3.5.2 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27     |

| Re | feren                                       | nces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28     |

|    | 0                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •••    |

| A  | Spec                                        | cification Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30     |

| B  | Cost                                        | t-Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31     |

| C  | Rep                                         | ositories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31     |

| D  | Verilog module for gain & offset control 32 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| E  | Pipe                                        | elining of PyRPL RTL code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34     |

|    | -                                           | ndling the BLOOD Server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34     |

| -  | 1                                           | <i>o</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

| G  | Doc                                         | cumentation for BLOOD-Devil client                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35     |

|    | G.1                                         | Integration of PyRPL client into Devil client                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35     |

|    | G.2                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36     |

|    | G.3                                         | The BloodChannel class                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37     |

|    | G.4                                         | Initialization of Server after power-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37     |

|    | G.5                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38     |

|   | G.6 Channel Detection process                                          | 38 |

|---|------------------------------------------------------------------------|----|

|   | G.7 Changes in the GUI                                                 | 38 |

|   | G.8 transferfunctionplot.py                                            |    |

|   | G.9 Server only registers used between client and server               |    |

|   | G.10 Communication between server DummyChannel and client BloodChannel |    |

| н | Detailed list of proposed code changes and missing features            | 42 |

|   | H.1 General Features                                                   | 42 |

|   | H.1.1 Entire System                                                    | 42 |

|   | H.1.2 Server                                                           |    |

|   | H.1.3 Client                                                           | 42 |

|   | H.2 Fixes for the Client                                               | 42 |

|   | H.2.1 main.py                                                          | 43 |

|   | H.2.2 bloodserver.py                                                   | 43 |

|   | H.2.3 bloodchannel.py                                                  | 43 |

|   | H.2.4 customwidgets.py                                                 | 44 |

|   | H.3 Server                                                             | 44 |

|   | H.3.1 DummyChannel.cpp                                                 | 44 |

|   | H.4 Bitstream                                                          | 44 |

|   | $H.5$ pyrpl_tiqi                                                       | 44 |

| I | Modifications that make the BloodClient incompatible with the EVIL     | 45 |

## 1 Introduction

## 1.1 Control in Trapped-Ion experiments

Trapped Ions are one of the leading platforms in the endeavour to implement different forms of Quantum Computing, from Universal QC to Quantum Simulation. The logic states are encoded in the energy-levels of single ions, trapped alone or with a manageable number of others in an electric (or sometimes also magnetic) field. The electronic energy levels of ions couple to the electromagnetic field surrounding the atom, and this coupling is used to prepare, manipulate and read out the state of an ion qubit. Practically, this means that the qubits can be controlled using laser light. Depending on the exact operation, the frequency, intensity and phase of this laser must be very precise, and feedback control is used to ensure any noise or drift is mitigated. Outside factors such as temperature and pressure fluctuations from sound waves negatively affect the laser's stability. As the linewidth of some energy levels used in trapped ion experiments can be very narrow, frequency stability is crucial, and additional layers of control have to be introduced to ensure this stability can be guaranteed even in a lab environment that includes temperature drifts or researchers working and moving in the vicinity of the experiment.

### 1.1.1 The PDH lock

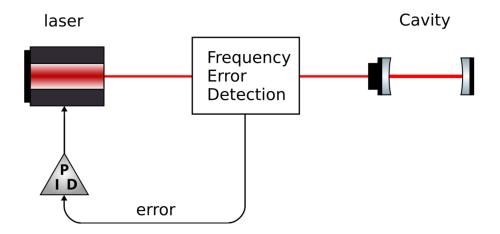

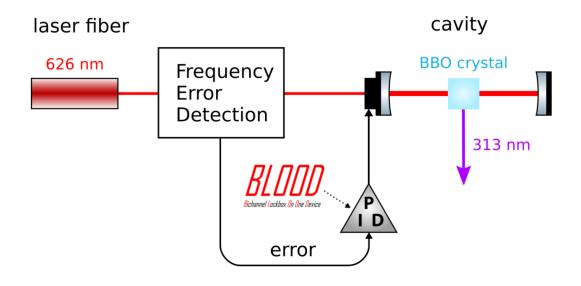

As an example, we discuss a way to stabilize the frequency of a laser making use of active feedback control. The basic idea is to measure the frequency difference between the laser and a very stable reference frequency. A common choice for this is the resonance frequency of a high-finesse cavity, which can be engineered to be sufficiently stable provided it is situated in a temperature controlled environment isolated from sound. A laser incident onto the cavity will only experience minimal reflection if its frequency matches a multiple of the resonance frequency. By measuring the reflection one can implement feedback control, changing the laser frequency until it reaches resonance. As the intensity of the reflected light is symmetric around the minimum, its phase must be used to determine the sign of the frequency error. This can practically be extracted by creating two side bands, symmetrically around the resonance. Their combined reflection signal will now depend on their relative phase shift, and thus also give away the direction of the detuning, which makes feedback control possible. This technique is called, after its inventors, the Pound-Drever-Hall (PDH) technique. [8] A schematic setup of an experimental implementation can be seen in Figure 1.

Figure 1: Example schematic of a PDH lock. In this case, the frequency of the laser is modified by adjusting the current through the laser diode or its temperature, dependent on the output of a PID controller that takes the demodulated reflection as an input.

## 1.2 State of the Art

## 1.2.1 Hardware

In the Trapped Ion Quantum Information (TIQI) lab, almost all tasks related to feedback based laser stabilization are performed using the "Electronically variable interactive lockbox", or "EVIL". It was designed by Ludwig de Clercq and Vlad Negnevitsky around 2012. It consists of a custom PCB with two analog input and output channels and the commercial Papilio One 500K FPGA board [3]. The signal processing is done digitally within the FPGA using a firmware which was also developed specifically for this device. The EVIL needs  $\pm 15$  V and GND supplies and its enclosure is designed to fit standard 19' racks.

A more detailed list of specifications can be found in Appendix A, together with a comparison of the device we have designed during this project.

### 1.2.2 Software

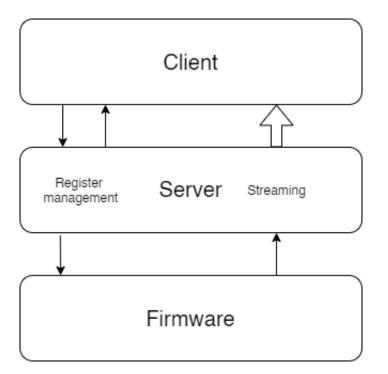

The current EVIL boards are controlled via a server that runs on a Raspberry Pi which is connected via USB to the EVIL boards. This server announces itself to a client running on a PC in the lab, from which the experiment is then controlled. Written by David Nadlinger [13] in 2015, this client-server setup supports a multi-client logic, that allows for multiple clients to connect to multiple servers simultaneously. Any parameter changes done by one client are synchronized to all others in real-time.

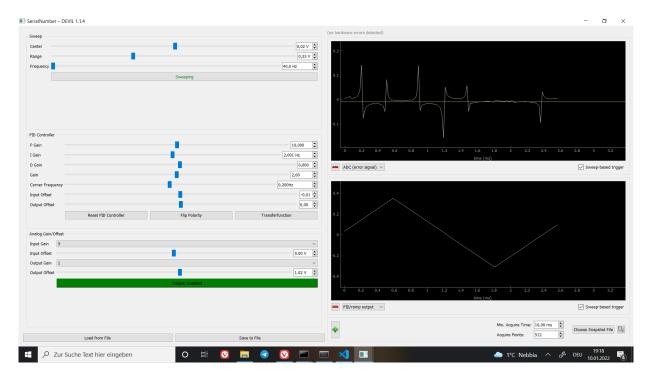

The client is written in Python and can be used directly from source or via a very simple executable for Windows. It comes with a simple GUI for experiment control, relying on the Python binding *PyQT* [18] of the Qt framework [21].

The server on the other hand is written in C++, and uses the *boost.asio* library [2] for asynchronous operations management. Communication over the network is implemented using the ZeroMQ library [26].

## 1.3 Reason for upgrade

The EVIL has been successfully used for many projects since it was introduced in 2015, but has become outdated since: The Papilio One 500K, which carries the FPGA, is no longer available. A total redesign of the EVIL would be necessary because the whole design is tailored around this part.

This also opens up the opportunity to improve upon some shortcomings of the EVIL. The offset and gain of the analog input stage can be adjusted by potentiometers on the PCB which are only reachable by unmounting the EVIL from the rack. Further points of improvement are the low 10-bit resolution of the ADC in the input stage followed by the few DSP units available on the Xilinx XC3S500E FPGA. The EVIL also only has a USB interface. To control the EVIL remotely over the Lab-network it is connected via USB to a Raspberry Pi which is then connected to the lab network [14]. It would be favorable to omit the Raspberry Pi by directly running the server on the EVIL. This requires a CPU which is able to run Linux.

Xilinx' Zynq SoC devices meet these demands, as they feature both ARM processing cores, networking interfaces as well as a much larger programmable logic with more DSP units on one chip.

## 1.4 **Project goals**

Drawing from years of experience using the DEVIL in the TIQI lab, our supervisors Martin Stadler, Nick Schwegler and Vlad Negnevitsky helped us to set the following goals:

- A system on chip with integrated FPGA and CPU which is capable of running Linux and the server. This approach provides a much simpler interface between FPGA and CPU while improving latency and throughput. This would most probably mean using a Xilinx Zynq chip as the central element of the lock box.

- A direct Ethernet connection, so that the server can communicate directly with the lab network.

- Clocking the ADCs with an crystal oscillator clock instead of an FPGA generated clock would lead to a better sampling and signal quality.

- A control loop bandwidth comparable to the old EVILs, which requires a latency below 1  $\mu s,$  with a target of 400 ns

- An input voltage range from 200 mV to 6 V and an output range from 2 to 10 V.

- The new device should be rack-mountable and require the same power supplies as the EVIL.

- Digitally controlled amplifier gains and offset voltages, adjustable directly via the control software (the client).

To match these expectations, we decided to base our solution on the readily available RedPitaya STEMlab 125-14 multipurpose boards [23], and design a custom carrier PCB around it to match the input/output specifications and add the analog gain and offset control. The STEMlab features a 14-bit ADC and DAC, a Xilinx Zynq 7010 SoC and provides most of the features we require, including Ethernet connectivity. The custom PCB can then be designed such that all other goals are met. The solution we went for was inspired by a lockbox designed by the 'Atoms - Photons - Quanta' research group at TU Darmstadt [17]. Starting from their design we modified it using multiplexers and digital potentiometers to allow for controlling the analog gain and offset using the multi-purpose I/O pins on the extension connector of the RedPitaya.

Sticking with the current naming tradition within the TIQI group, we propose to call our device **BLOOD** - **B**ichannel Lockbox **On O**ne **D**evice. We also came up with a logo for the BLOOD (Fig. 2).

Having decided for the type of solution we want to propose early in the project, most of the work will go into designing the carrier board, and writing the software and firmware necessary to provide the required features.

Figure 2: The official logo of the BLOOD.

## 2 Execution

### 2.1 The Printed Circuit Board

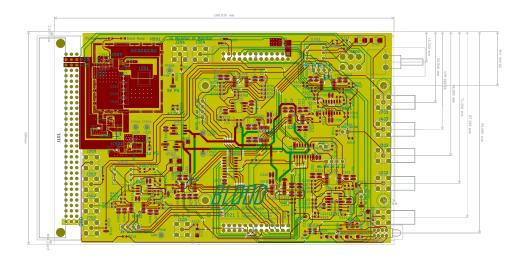

In this subsection we present the design of the printed circuit board. Firstly, the schematics will be illustrated, then the layout and finally the soldering process.

### 2.1.1 Schematics

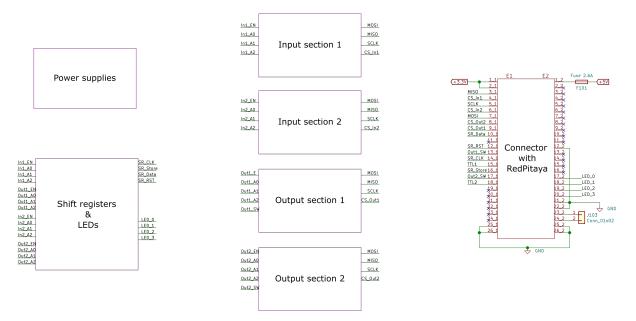

Figure 3: Main blocks of the schematics and their interconnections, adapted from the main page of the KiCad schematics.

Our schematics are based on the open source project *RedPitaya-IntStab* [24] which uses KiCad, a CAD software for drawing schematics and layouting PCBs.

In Figure 3 you can see the main blocks that compose our design:

<u>Power supplies</u>: The block contains the connections to the external power supply which provides  $\pm 15$  V and ground. It also contains the voltage converter circuits to generate the required voltages for the active components on the carries.

Connector with RedPitaya: On the right side of Fig. 3 there are all the pins that come from the two extension connectors (E1 and E2) of the RedPitaya. These pins have a few different functions. First of all, the RedPitaya can be powered by applying 5 V to pin 1 of E2. 3.3V are provided by the RedPitaya through pin 1 and 2 of E1. The pins SCLK, MISO, MOSI, CS\_In1,2 and CS\_Out1,2 are used to communicate with the digital potentiometers in the input and output sections. The pins SR\_Data, SR\_RST, SR\_CLK, SR\_Store are used to control the two 8-bits shift registers in the "Shift registers & LEDs" block. Out1\_SW and Out2\_SW are used to control the output switches that enable and disable the two outputs. TTL1 and TTL2 are intended to be used as trigger inputs or outputs. Lastly on E2 LED\_0-3 are used to control the 4 LEDs in the "Shift registers & LEDs" block.

Input and Output Sections: In the centre of figure 3 there are four blocks, two are input blocks and two are output blocks. The input blocks contain the components that act on the input signals before they enter the RedPitaya. The output blocks contain the components that condition the signals that come out of the RedPitaya.

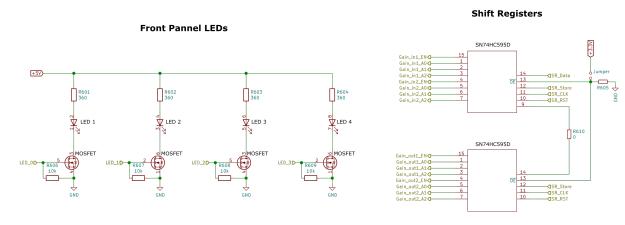

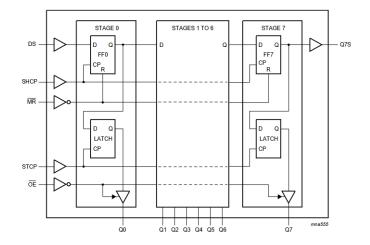

Shift Registers & LEDs: This last block serves two purposes:

- Fan out 4 signals to 16 using two 8-bit shift registers inside that take as inputs the SR\_Data, SR\_RST, SR\_CLK, SR\_Store signals from the RedPitaya and output 16 signals (all the signals on the left side of the block in figure 3) which are used to control the 4 multiplexers, one in every input/output block.

- Provide visual feedback in the lab using 4 LEDs which are visible from the front panel of the BLOOD and can be turned ON and OFF through the signals LED\_0-3 coming from the RedPitaya.

### **Power Supply section**

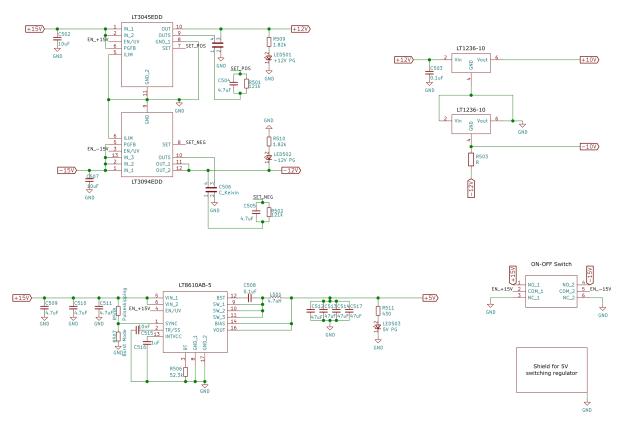

As written above, in this section of the schematics there are the components that convert the +/-15V provided to the PCB from the laboratory into the voltages necessary for the other components of the PCB. Figure 4 shows a simplified version of the KiCad schematics.

Figure 4: Schematics of the power supplies, adapted from the KiCad schematics.

Starting from the top left of the figure, the two components LT3045EDD and LT3094EDD are high performance low dropout linear regulators with ultralow noise and ultrahigh power supply rejection ratio (PSRR) architecture. The output of these devices is set to +/-12V and they can supply up to 500mA each [6]. These voltages are needed for supplying the OpAmps, digipots and multiplexers in the input and output sections.

On the bottom left of figure 4, the component LT8610AB-5 is a compact and high efficiency synchronous step-down switching regulator that has high maximum output currents of 3.5A [7]. This step down regulator provides 5V for powering the RedPitaya through the connector E2 and the LEDs that are on the PCB. In order to reduce the output ripple to less than 10mV we added four 47uF capacitors at the output. The switching frequency has been set to 800KHz through the resistor R506.

On the top right of the figure, the two LT1236-10 are precision references that combine ultralow drift and noise and high output accuracy [5]. The maximum output current that they can source and sink is up to 10mA. The low drift and noise and high output accuracy are important properties for these components because the +/-10V they supply is used by the digital potentiometers in the input/output sections to adjust the voltage offset. The voltage offset needs to be very stable in time for the PID controller to work

effectively.

At the bottom right of figure 4 there is the ON-OFF switch which acts on all the power supply chips at the same time. It turns them on by connecting the respective enable pins to the input voltage (+/-15V) and off by connection the enable pins to GND. The last component is a metal shield which covers the 5V switching regulator to reduce the switching noise that leaks out.

As a last remark we added 3 LEDs respectively at the +5V and +/-12V outputs which indicate whether the respective chip is ON or OFF.

### **Input Section**

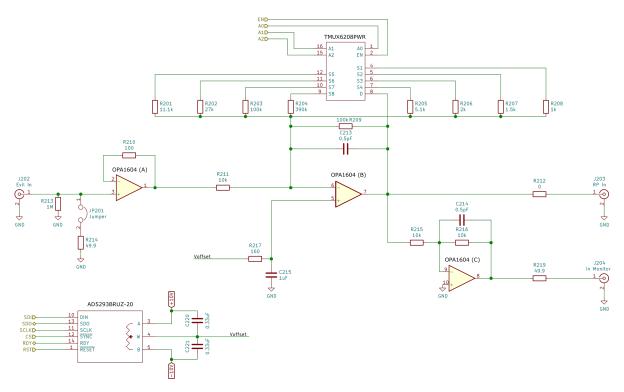

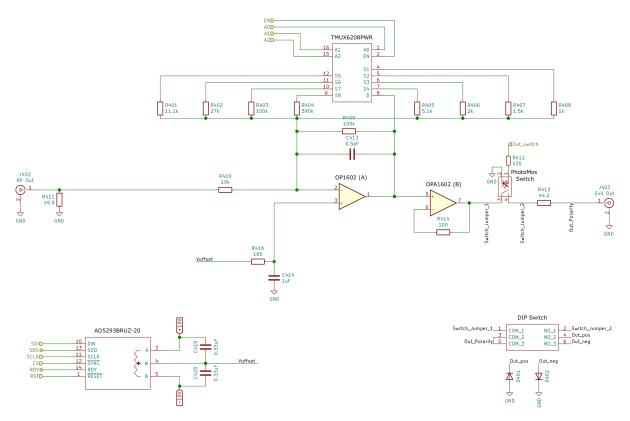

Figure 5: Schematics of the input section, adapted from the KiCad schematics.

On the device there are two analog signal inputs. Each one of these inputs goes through one of the two identical input sections on the PCB. In figure 5 there are the schematics which are a simplified version of the ones from KiCad.

The main features that we implemented in the input section are:

- Variable gain

- Variable offset

- The input impedance is  $1 M\Omega$  by default and can be changed to  $50 \Omega$  with a jumper (JP201)

- The analog input signal of the RedPitaya can be monitored from J204 without disturbing it

Variable gain: This feature is achieved thanks to the precision multiplexer TMUX6208PWR [11]. This component allows to select one of the eight different resistors (R201-R208) on the feedback path of the operational amplifier OPA1604 (B) which is in inverting configuration. The resistor is selected through the signals A2, A1, A0 which correspond to the binary address of the desired resistor, starting from 000 for the first one. For example to select the resistor number 3 (A2,A1,A0)=(0,1,1). The signals EN (EN enables or disables the MUX), A2, A1, A0 come from one of the two shift registers (see 2.1.1) which are in turn controlled by the RedPitaya.

| $R_{mux}$ [k $\Omega$ ] | G    |

|-------------------------|------|

| 1                       | 0.1  |

| 1.5                     | 0.15 |

| 2                       | 0.2  |

| 5.1                     | 0.49 |

| 11.1                    | 1    |

| 27                      | 2.13 |

| 100                     | 5    |

| 390                     | 7.96 |

| Mux off                 | 10   |

Table 1: Table of all possible values that *G* can have, according to Eq. 2.1.

<u>Variable offset</u>: This feature is achieved thanks to the digital potentiometer AD5293BRUZ-20 [4]. The resistance between the pins A and B of this component is  $20 k\Omega$ . The wiper can be adjusted in 1024 different positions between A and B. By inputting the voltage references +/-10V in A and B, the pin W can be set to a voltage that ranges from -10V to +10V. The position of the wiper is sent to the digipot through an SPI interface. The offset voltage coming from W (wiper) is inputted to the + pin of the OPAMP OPA1604 (B).

In this configuration the signal coming out of this opamp (B) is:

$$V_{out} = -GV_{in} + (G+1)V_{offset}$$

(2.1)

where  $G = \frac{R_{feedback}}{R211}$  with  $R_{feedback}$  equal to R209 in parallel with the resistor selected by the multiplexer. Tab 1 shows all the possible gain values that can be selected.

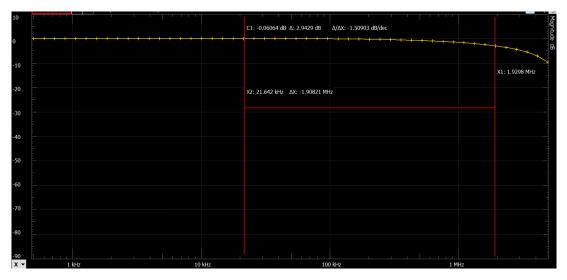

We simulated the whole circuit in PSpice for TI. We had to use a SPICE simulator from TI because a SPICE model for the OPA1602/1604 was only available from within Texas Instruments software. The TMUX6208PWR does not come with a SPICE model, so we used the model of an almost equivalent multiplexer, the ADG1408. The capacitor C213 was chosen such that the transfer function of the amplifier stage has maximum bandwidth and a flat response. We also used the PSpice simulation to determine the power consumption of the whole circuit.

#### **Output Section**

As for the inputs, on the PCB there are two identical output sections. See figure 6 for the schematics which are an adaptation of the one from KiCad.

The working principles of the output sections are very similar to the ones of the inputs. The variable gain and offset are obtained in the same way. Other features implemented in these sections are:

- The output can be enabled or disabled from the RedPitaya and is disabled by default. This allows to enable the output only if the user is sure that the output voltage is in the accepted range of the equipment that is connected to the device.

- It is possible to select the voltage range of the output as only positive or only negative through a DIP-Switch.

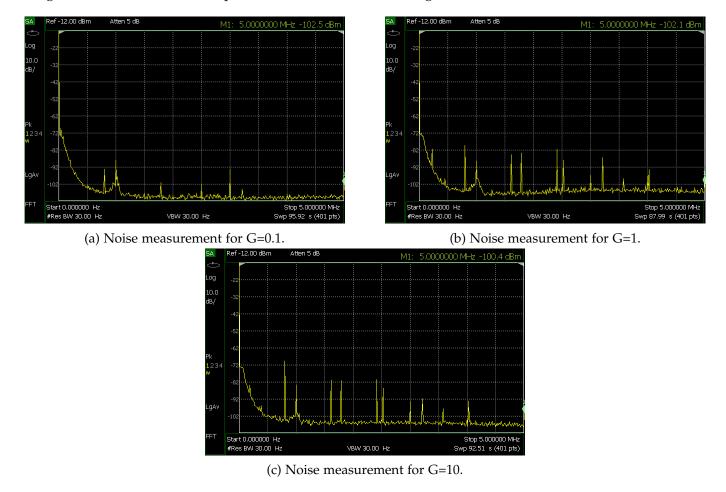

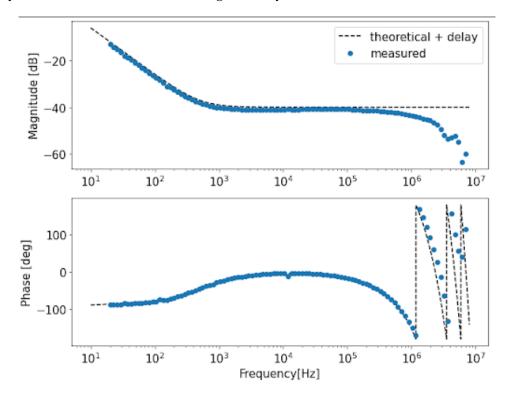

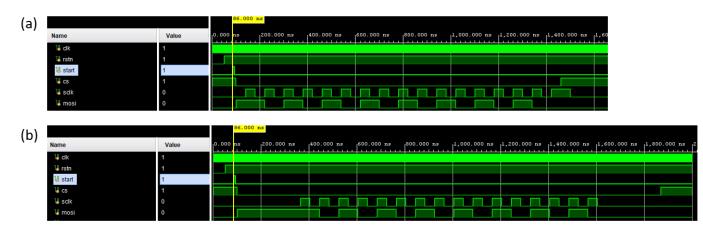

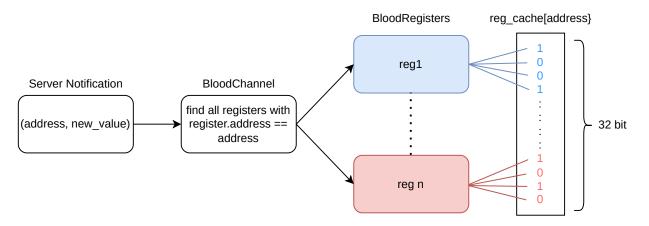

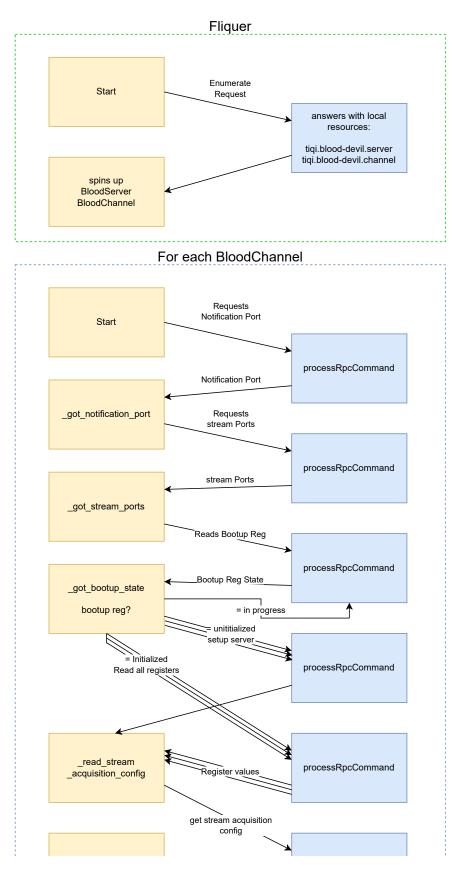

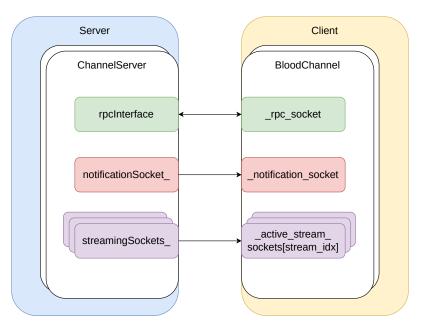

Output enable and disable: this feature is provided by the use of the PhotoMOS switch AQY221N3MY [16] in series with the output. Pin 1 of this component is controlled by the RedPitaya board and, when it is high, it closes pins 3 and 4, enabling the output.